**PRODUCT DESCRIPTION**

**µPD 7281**

**IMAGE PIPELINED PROCESSOR

APPLICATION LIBRARY**

NEC ELECTRONICS (EUROPE) GMBH

PRODUCT DESCRIPTION

$\mu$ PD7281

IMAGE PIPELINED PROCESSOR

APPLICATION LIBRARY

5/85 V1.0

**VOLUME I**

**BINARY IMAGE PROCESSING**

## Table of Contents

|                                                               |    |

|---------------------------------------------------------------|----|

| Introduction .....                                            | 1  |

| Chapter 1: System Configuration .....                         | 3  |

| Chapter 2: Block Transfer .....                               | 5  |

| 2.1 Word Boundary Transfer .....                              | 5  |

| 2.1.1 Processing Explained .....                              | 5  |

| 2.1.2 Algorithm .....                                         | 5  |

| 2.1.3 Parameters and Their Applicable Ranges .....            | 6  |

| 2.1.4 Flow Graph Explained .....                              | 7  |

| 2.1.5 Tips on Writing Flow Graphs .....                       | 9  |

| 2.1.6 Assembler Source Listing .....                          | 15 |

| Chapter 3: Logical Operation .....                            | 13 |

| 3.1 NOT (Single-Operand Operation) .....                      | 13 |

| 3.1.1 Processing Explained .....                              | 13 |

| 3.1.2 Algorithm .....                                         | 13 |

| 3.1.3 Parameters and Their Applicable Ranges .....            | 13 |

| 3.1.4 Flow Graphs Explained .....                             | 14 |

| 3.1.5 Tips on Writing Flow Graphs .....                       | 16 |

| 3.1.6 Assembler Source Listing .....                          | 16 |

| 3.2 AND, OR, Exclusive OR (Double-Operand Operations) .....   | 18 |

| 3.2.1 Processing Explained .....                              | 18 |

| 3.2.2 Algorithm .....                                         | 18 |

| 3.2.3 Parameters and Their Applicable Ranges .....            | 18 |

| 3.2.4 Flow Graph Explained .....                              | 19 |

| 3.2.5 Tips on Writing Flow Graphs .....                       | 21 |

| 3.2.6 Assembler Source Listing .....                          | 21 |

| Chapter 4: Enlargement and Shrinking .....                    | 23 |

| 4.1 Simple One-Half Shrinking .....                           | 23 |

| 4.1.1 Processing Explained .....                              | 23 |

| 4.1.2 Algorithm .....                                         | 23 |

| 4.1.3 Parameters and Their Applicable Ranges .....            | 24 |

| 4.1.4 Flow Graph Explained .....                              | 26 |

| 4.1.5 Tips on Writing Flow Graphs .....                       | 30 |

| 4.1.6 Assembler Source Listing .....                          | 30 |

| 4.2 Four-Point OR One-Half Shrinking .....                    | 33 |

| 4.2.1 Processing Explained .....                              | 33 |

| 4.2.2 Algorithm .....                                         | 33 |

| 4.2.3 Parameters and Their Applicable Ranges .....            | 34 |

| 4.2.4 Flow Graph Explained .....                              | 35 |

| 4.2.5 Tips on Writing Flow Graphs .....                       | 40 |

| 4.2.6 Assembler Source Listing .....                          | 42 |

| 4.3 Neighboring 16-Point Addition One-Quarter Shrinking ..... | 45 |

| 4.3.1 Processing Explained .....                              | 45 |

| 4.3.2 Algorithm .....                                         | 45 |

| 4.3.3 Parameters and Their Applicable Ranges .....            | 47 |

| 4.3.4 Flow Graph Explained .....                              | 48 |

| 4.3.5 Assembler Source Listing .....                          | 51 |

|                                               |                                                           |           |

|-----------------------------------------------|-----------------------------------------------------------|-----------|

| 4.4                                           | Simple Double Enlargement .....                           | 55        |

| 4.4.1                                         | Processing Explained .....                                | 55        |

| 4.4.2                                         | Algorithm .....                                           | 55        |

| 4.4.3                                         | Parameters and Their Applicable Ranges .....              | 56        |

| 4.4.4                                         | Flow Graph Explained .....                                | 57        |

| 4.4.5                                         | Assembler Source Listing .....                            | 60        |

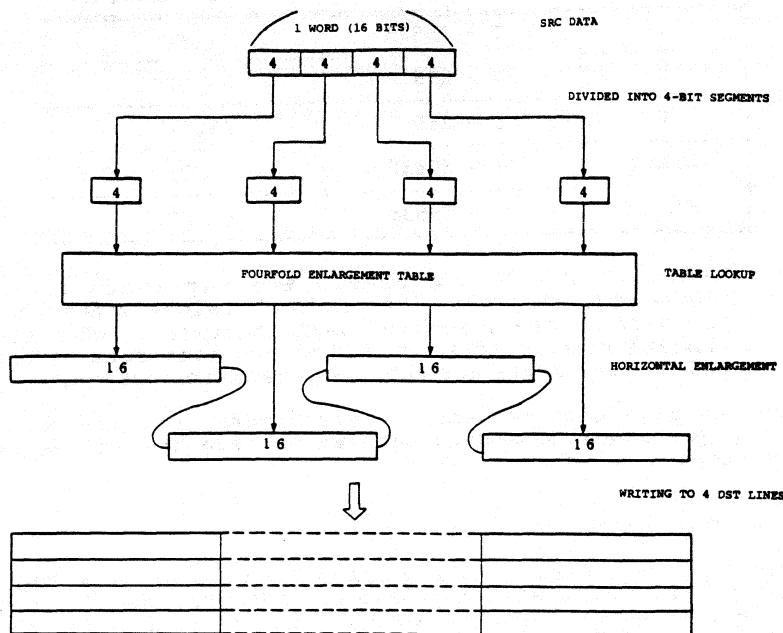

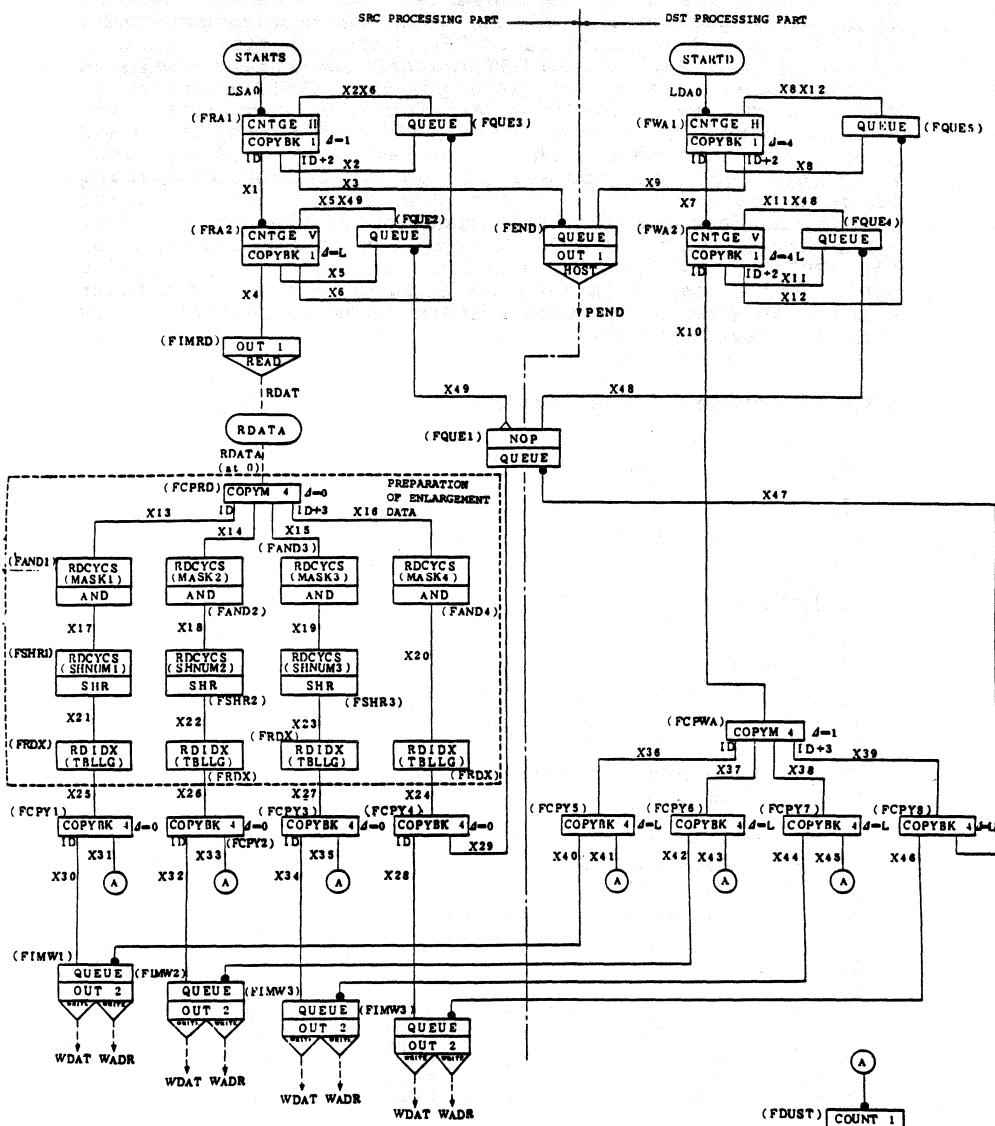

| 4.5                                           | Simple Quadruple Enlargement .....                        | 64        |

| 4.5.1                                         | Processing Explained .....                                | 64        |

| 4.5.2                                         | Algorithm .....                                           | 64        |

| 4.5.3                                         | Parameters and Their Applicable Ranges .....              | 65        |

| 4.5.4                                         | Flow Graph Explained .....                                | 66        |

| 4.5.5                                         | Tips on Writing Flow Graphs .....                         | 68        |

| 4.5.6                                         | Assembler Source Listing .....                            | 68        |

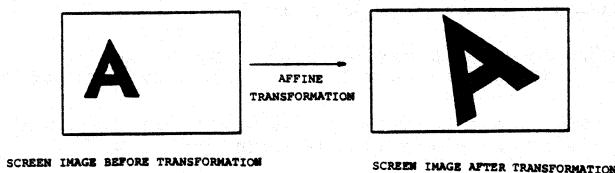

| <b>Chapter 5: Affine Transformation .....</b> |                                                           | <b>71</b> |

| 5.1                                           | Processing Explained .....                                | 71        |

| 5.2                                           | Algorithm .....                                           | 71        |

| 5.3                                           | Parameters and Their Applicable Ranges .....              | 75        |

| 5.4                                           | Flow Graph Explained .....                                | 77        |

| 5.5                                           | Tips on Writing Flow Graphs .....                         | 79        |

| 5.6                                           | Assembler Source Listing .....                            | 79        |

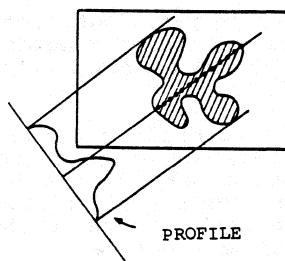

| <b>Chapter 6: Profiling .....</b>             |                                                           | <b>83</b> |

| 6.1                                           | Horizontal Profiling .....                                | 83        |

| 6.1.1                                         | Processing Explained .....                                | 83        |

| 6.1.2                                         | Algorithm .....                                           | 83        |

| 6.1.3                                         | Parameters and Their Applicable Ranges .....              | 85        |

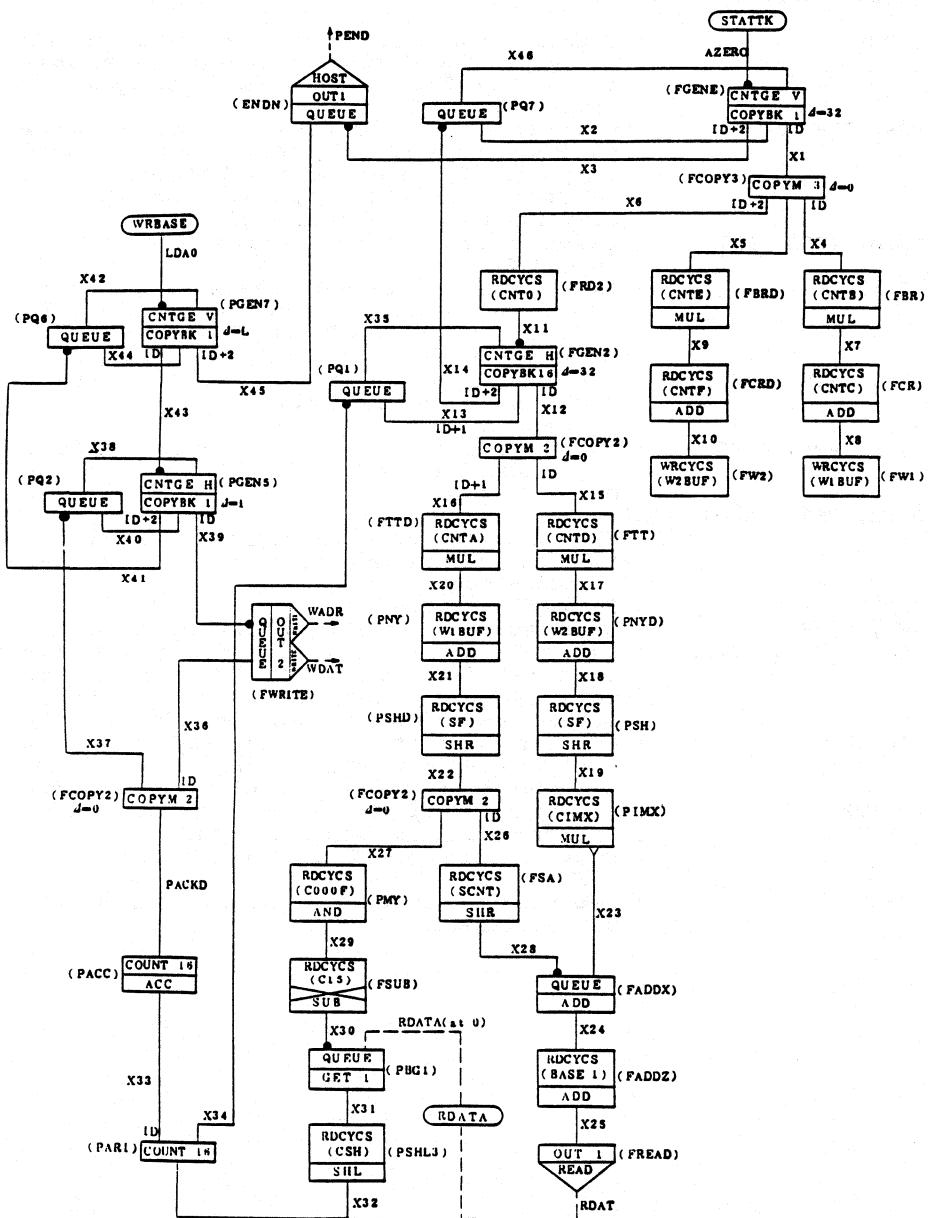

| 6.1.4                                         | Flow Graph Explained .....                                | 86        |

| 6.1.5                                         | Assembler Source Listing .....                            | 89        |

| 6.2                                           | Vertical Profiling .....                                  | 91        |

| 6.2.1                                         | Processing Explained .....                                | 91        |

| 6.2.2                                         | Algorithm .....                                           | 91        |

| 6.2.3                                         | Parameters and Their Applicable Ranges .....              | 93        |

| 6.2.4                                         | Flow Graph Explained .....                                | 94        |

| 6.2.5                                         | Assembler Source Listing .....                            | 97        |

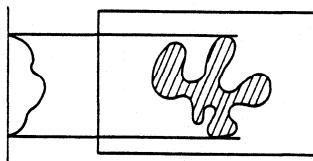

| <b>Chapter 7: 3 x 3 Masking .....</b>         |                                                           | <b>99</b> |

| 7.1                                           | Common Processing (Image Memory Address Generation) ..... | 99        |

| 7.1.1                                         | Processing Explained .....                                | 99        |

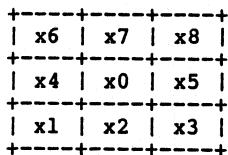

| 7.1.2                                         | Algorithm .....                                           | 100       |

| 7.1.3                                         | Parameters and Their Applicable Ranges .....              | 102       |

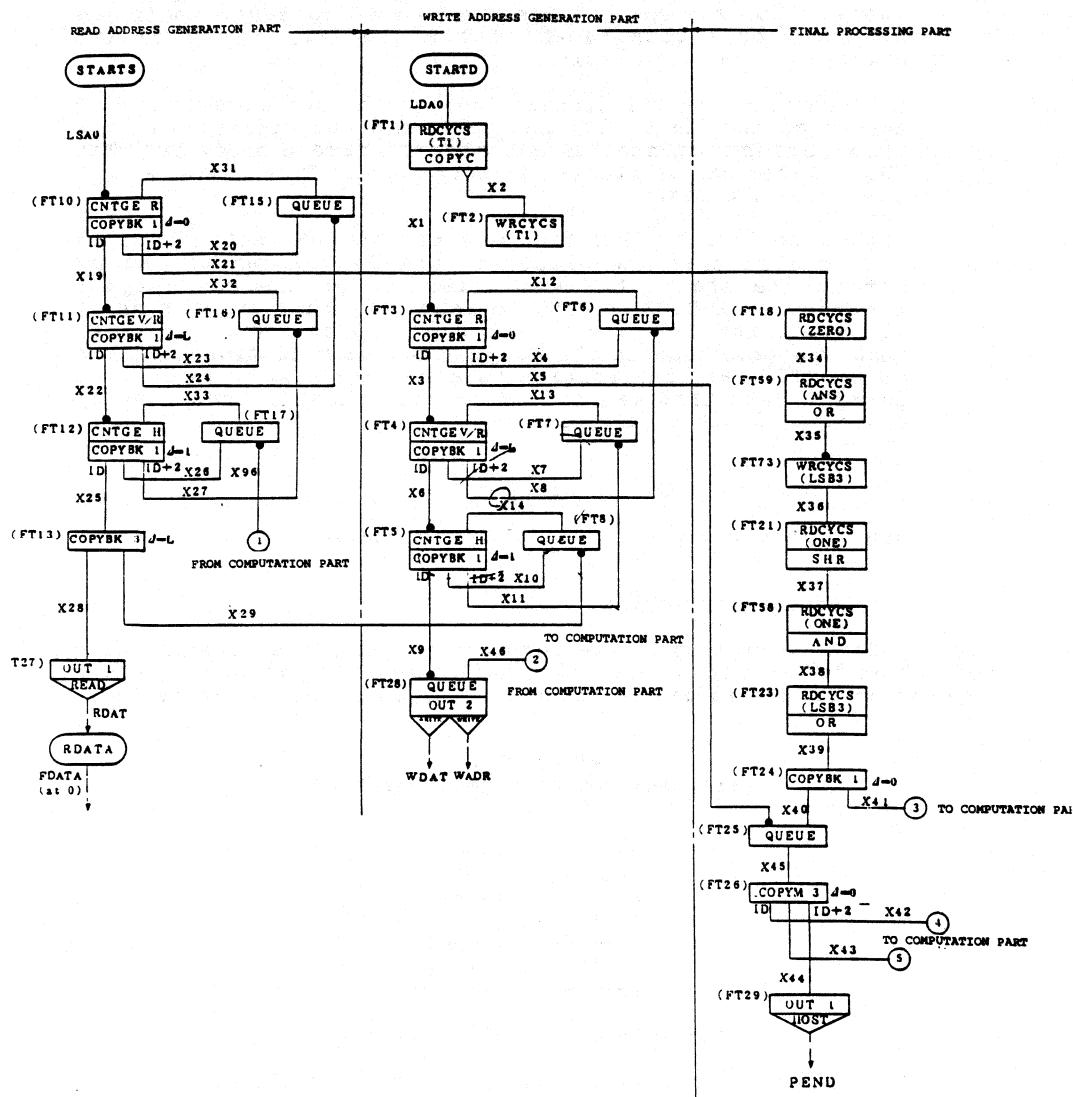

| 7.1.4                                         | Flow Graph Explained .....                                | 103       |

| 7.1.5                                         | Tips on Writing Flow Graphs .....                         | 106       |

| 7.1.6                                         | Assembler Source Listing .....                            | 106       |

| 7.2                                           | Mask Operations .....                                     | 106       |

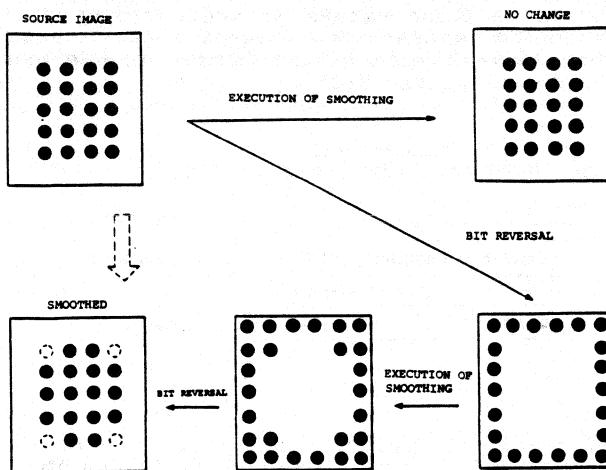

| 7.2.1                                         | Smoothing .....                                           | 107       |

| 7.2.1.1                                       | Processing Explained .....                                | 107       |

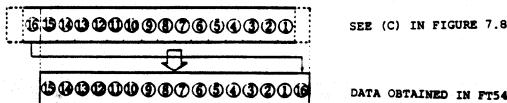

| 7.2.1.2                                       | Algorithm .....                                           | 108       |

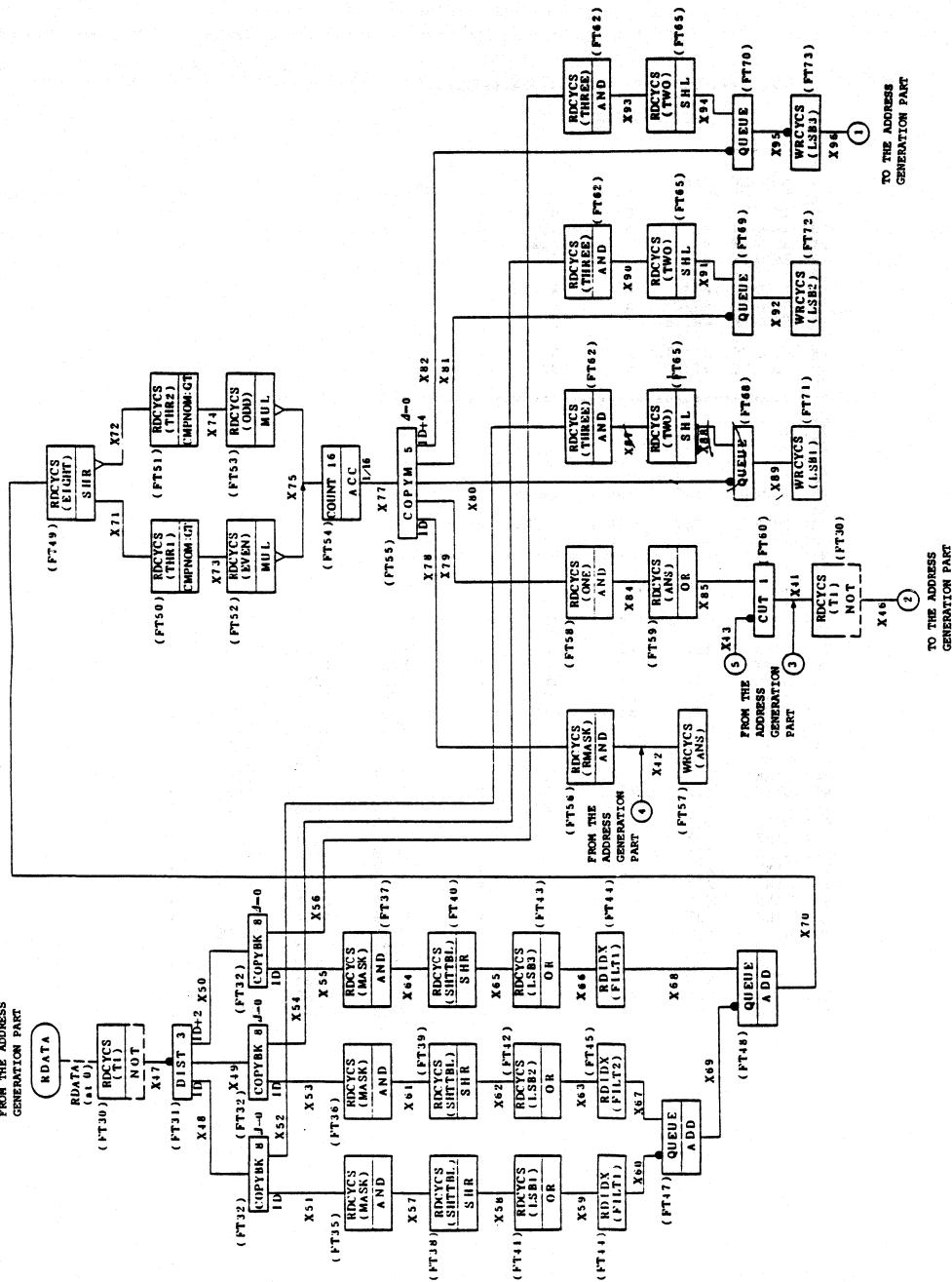

| 7.2.1.3                                       | Flow Graph Explained .....                                | 111       |

| 7.2.1.4                                       | Assembler Source Listing .....                            | 114       |

| 7.2.2                                         | Thinning .....                                            | 118       |

| 7.2.2.1                                       | Processing Explained .....                                | 118       |

| 7.2.2.2                                       | Algorithm .....                                           | 118       |

| 7.2.2.3                                       | Flow Graph Explained .....                                | 121       |

| 7.2.2.4                                       | Tips on Writing Flow Graphs .....                         | 124       |

|                                           |                                |     |

|-------------------------------------------|--------------------------------|-----|

| 7.2.2.5                                   | Assembler Source Listing ..... | 124 |

| 7.2.3                                     | Edge Detection .....           | 129 |

| 7.2.3.1                                   | Processing Explained .....     | 129 |

| 7.2.3.2                                   | Algorithm .....                | 129 |

| 7.2.3.3                                   | Flow Graph Explained .....     | 131 |

| 7.2.3.4                                   | Assembler Source Listing ..... | 133 |

| Appendix A: Image Memory Read/Write ..... |                                | 137 |

**Notice:**

- (1) The contents of this application library may not be copied wholly or in part.

- (2) Information contained in this application library is subject to change without notice.

- (3) This application library has been prepared with utmost care; however, if you have questions or find errors or omissions in it, please notify NEC Electronics, USA.

- (4) Notwithstanding the statement in item (3) above, NEC Electronics is not responsible for any damage resulting from an execution of the contents of this document.

## Introduction

The uPD7281 incorporates a configuration which is quite different from those of other microcomputers, and most readers may be unfamiliar with its program development facilities. The uPD7281 Application Library is a collection of programs that provide specific examples of programming on the uPD7281. The document is intended as a guide to learning uPD7281 programming methods and techniques.

This Application Library (Volume I) addresses "Binary Image Processing," which is one of the application areas of the uPD7281. The applications presented in the following pages include:

- \* Block Transfer

- Word Boundary Transfer

- \* Logical Operations

- NOT (single-operand operations)

- AND/OR/Exclusive OR (double-operand operations)

- \* Enlargement/Shrinking

- Simple 1/2 Shrinking

- 4-Point OR 1/2 Shrinking (Logical Addition)

- Neighboring 16-Point Addition 1/4 Shrinking (the Majority Rule)

- Simple Double Enlargement

- Simple Quadruple Enlargement

- \* Affine Transformation

- \* Profiling

- Horizontal

- Vertical

- \* 3 x 3 Masking

- Smoothing

- Thinning

- Edge Detection

Each example is discussed in terms of the following items:

- (1) Processing

- (2) Algorithm

- (3) Parameters and their applicable ranges

- (4) Flow graphs

- (5) Tips on preparing flow graphs

- (6) Assembler source listing

This Application Library explains uPD7281 programming methods. The reader is advised to consult the following publications for information on the uPD7281 itself and the assembler:

- (1) uPD7281 User's Manual

- (2) uPD7281 Software Package Operating Manual

In addition, the following document may be helpful:

- (3) uPD9305 (uPD7281 Peripheral LSI) User's Manual

**Note:**

This document is intended solely as an explanation of uPD7281 programming methods. The programming examples provided have not been tested on an actual system, and no claim is made for their validity.

### System Configuration

The programs included in this Application Library have been written with the assumption that they will be executed on a system configured as shown in Figure 1-1. A characteristic of this system is the use of a  $\mu$ PD7281 peripheral LSI, the  $\mu$ PD9305. This means that a  $\mu$ PD9305-defined token is used in accessing the image memory (IM). The programs presented in this document are not directly applicable to those systems in which a  $\mu$ PD9305 is not employed.

Although the programs shown in this document are written for a single  $\mu$ PD7281, the  $\mu$ PD9305 permits the use of several  $\mu$ PD7281s. Therefore, it is possible to increase the processing speed by partitioning the memory area among several  $\mu$ PD7281s, each running the same program. In such a case, the input token into the  $\mu$ PD7281s should be set up in accordance with the memory area to which it is assigned.

Figure 1-1

System Configuration

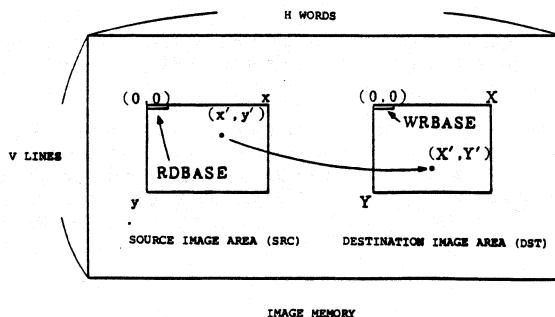

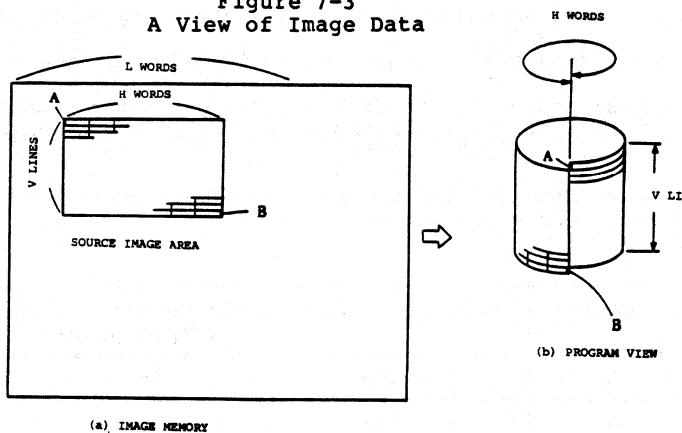

The following is a description of image memory configuration.

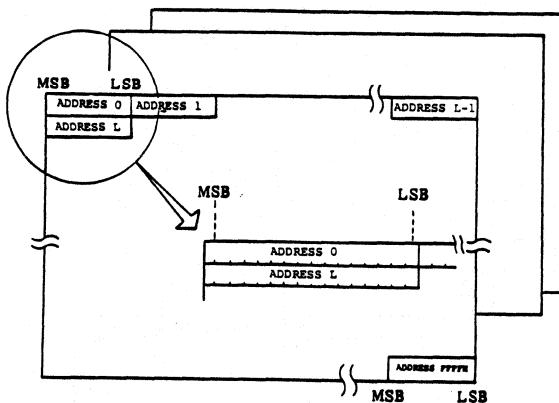

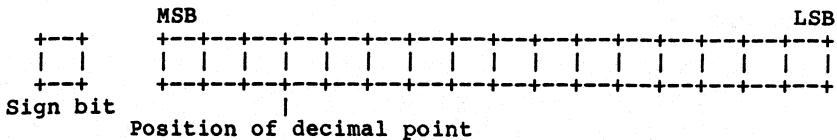

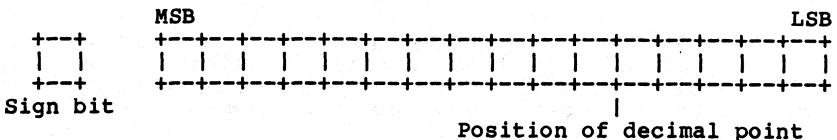

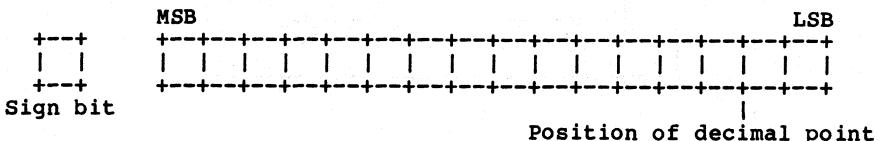

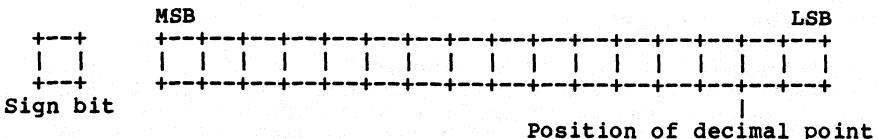

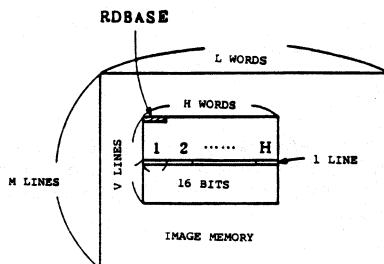

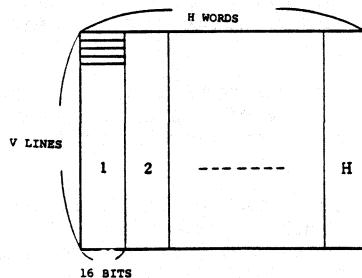

Shown in Figure 1-2 is an image memory configuration of the system addressed in this document. Viewing the memory in terms of screen display, the upper left corner of the screen corresponds to the most significant bit (MSB); this has the address of 0. The lower right corner the least significant bit (LSB); this has the address FFFFH\*. Since there are 16 bits in a word, if there are L words in a horizontal line, the number of picture elements (pixels) present in that line is  $16 \times L$  dots.

In this system the addresses 0 through FFFFH comprise a screen image (one bank). However, since the 8 high order bits of the 24 image memory address bits of the uPD9305 are not set (i.e., neither the bank-defining read high address or write high address is set), it is necessary to set up a high address register in the uPD9305 to use multiple banks. For the same reason, the addressable memory space of these programs is addresses 0 through FFFFH, both for source and destination images.

Figure 1-2

Image Memory Configuration

\* : This image memory configuration is different from that of the graphic display controllers uPD7220 and uPD7220A offered by NEC.

## Chapter 2

### Block Transfer

In this chapter we consider a program for transferring a specified rectangular area to another one. Although such a transfer can be accomplished with the same results by using a special case of the affine transformation (horizontal move), the method described below employs a different algorithm to reduce processing time. A discussion of word boundary transfer follows.

#### 2.1 Word Boundary Transfer

##### 2.1.1 Processing Explained

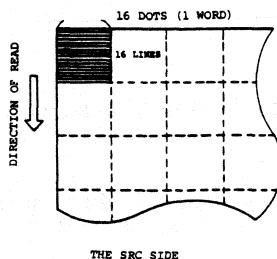

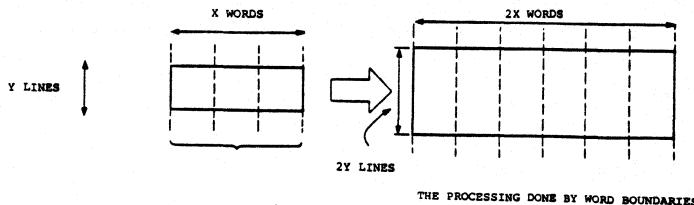

A word boundary transfer is a block-oriented transfer in which a rectangular area defined by 16 horizontal dots (comprising a word specified by the image memory address) and 16 vertical dots are transferred as a block of data. Although the minimum size of the transfer block ( $16 \times 16$  dots) cannot be varied, the program permits variations in horizontal screen size  $L$  (number of words), and the number of horizontal blocks  $H$  and vertical blocks  $V$  to be transferred.

##### 2.1.2 Algorithm

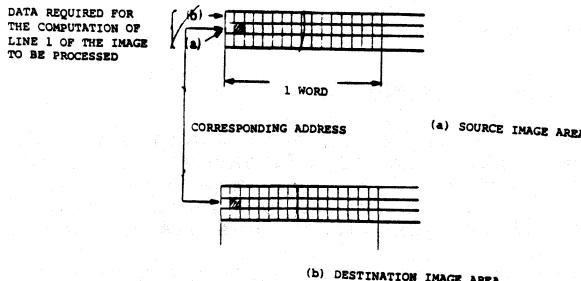

(1) First, the program and the constants are downloaded to the uPD7281. This is followed by the input from the host computer of two start-up tokens: the starting address (STARTS) of a source image area (SRC), and the starting address (STARTD) of the destination image area (DST).

Figure

(2) One block of data (SRC data) is read vertically, starting from the address indicated by STARTS.

(3) Simultaneously, one block of memory addresses needed for the storage of SRC data is generated, starting at the address indicated by STARTD.

(4) The SRC data is then written into the DST of the image memory in accordance with the corresponding DST addresses.

(5) When all of V blocks have been transferred by repeating this operation vertically, the process is repeated in the horizontal direction by incrementing the horizontal address by 1.

(6) The transfer operation is terminated when step (5) is completed for all H blocks in the horizontal direction.

Figure 2-1

An Example of Data Transfer (for H=6, V=4)

### 2.1.3 Parameters and Their Applicable Ranges

<Assembler-coded parameters>

L ... Number of image memory words in horizontal direction

H ... Number of source image area words in horizontal direction

V ... Number of source image area blocks in vertical direction

<Start-up token-defined parameters>

STARTS: Starting address of the source image area

STARTD: Starting address of the destination image area

The allowable values of these parameters are indicated in the table below:

| Parameter | Applicable range | (Value set in the example program) |

|-----------|------------------|------------------------------------|

| L         | 0 - 65535        | (64)                               |

| H         | 1 - 256          | (32)                               |

| V         | 1 - 256          | (32)                               |

| STARTS    | 0 - 65535        | ( 0 ) *                            |

| STARTD    | 0 - 65535        | (32) *                             |

\* : Although STARTS and STARTD are variables (i.e., addresses), they are given default values since they are used in the assembler DATA statement. When the uPD7281 is started up, the starting addresses of the SRC and DST areas are input as execution tokens.

Furthermore, H and V should be defined with care, since this program does not accommodate the switching of banks.

#### 2.1.4 Flow Graph Explained

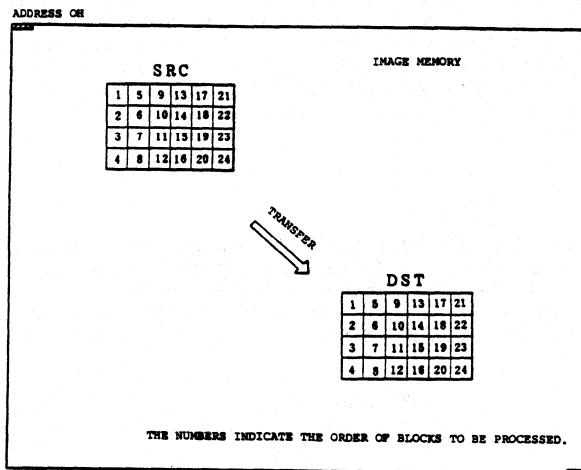

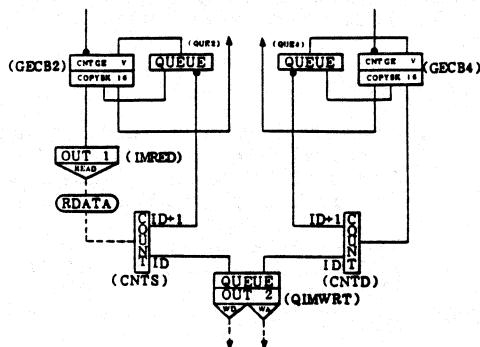

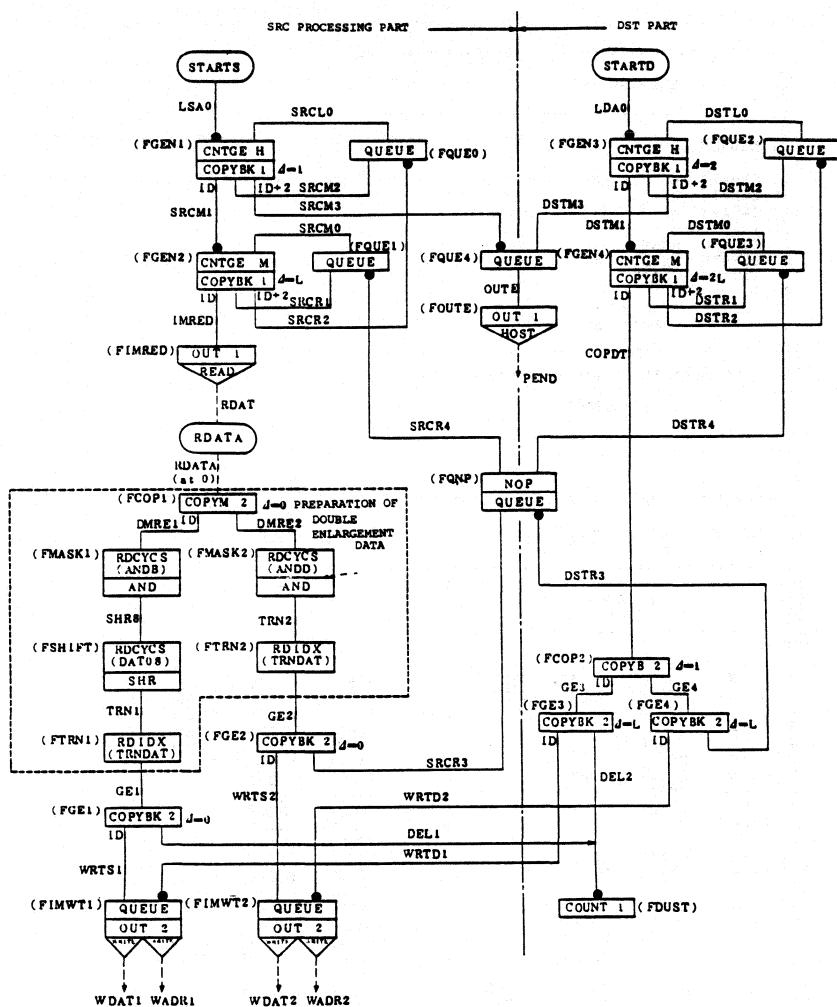

A word boundary transfer is divided into the SRC processing part and the DST processing part, as shown in Figure 2-2.

In Figure 2-2, GECB2 generates 16 (1 block) vertical direction addresses for each of the V blocks. Upon completion of the processing of V blocks of data in the vertical direction, GECB1 increments the address by 1 (corresponding to one block in the horizontal direction), and executes GECB2 again. The GECB2 thus executed repeats the vertical direction processing in the same manner. This combination of vertical and horizontal processing creates a set of addresses comprising a rectangular area of H x V blocks.

Figure 2-2

Word Boundary Transfer Flow Graph

The image memory data (SRC data) indicated by these addresses are read on the SRC side and written to the output address generated on the DST side. Further, since data are read on SRC and written to DST, SRC and DST are made to synchronize their actions so that the level of QIMWRT will not exceed 16.

#### <Explanation of Nodes>

|                   |                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------|

| GECB1/GECB3       | : Generate the starting address of V vertical blocks of the SRC/DST.                                 |

| GECB2/GECB4       | : Generate the addresses within the V vertical blocks of the SRC/DST.                                |

| IMRED             | : Reads SRC data.                                                                                    |

| QIMWRT            | : Writes data to DST.                                                                                |

| OUT               | : Indicates completion of data transfer to the host.                                                 |

| CNTS, CNTD, QNOP: | Synchronize processing between the SRC and DST.                                                      |

| QUE1/QUE3         | : Synchronize the actions of GECB1 and GECB3 so that addresses are generated for V blocks at a time. |

| QUE2/QUE4         | : Synchronize the actions of GEB2 and GEB4 so that addresses are generated for one block at a time.  |

| QUE5              | : Synchronizes SRC and DST to verify completion of their processing tasks.                           |

#### 2.1.5 Tips on Writing Flow Graphs

A program for word boundary data transfer is made up of an address generation part to read from the SRC side and an address generation part to write to the DST side. These parts are identical except for the portion that concerns the reading of SRC data.

The SRC processing part generates addresses and reads SRC data from the image memory, whereas the DST processing part is involved only in the preparation of addresses. For this reason, the SRC part works slower than the DST part does. If a synchronizing node (QNOP) was not provided, as in the case of Figure 2-3(a), the DST addresses would be created one after another asynchronously with the SRC address generation and tokens sent by DST would cause an overflow in the QIMWRT node. To prevent this overflow, a node, QNOP, in Figure 2-2, is required to synchronize the SRC and DST parts.

Figure 2-3 (a)

Overflow Caused by Difference in Processing Speeds

between SRC and DST

To synchronize these two processing parts, the scheme indicated in Figure 2-3 (b) might suffice and would also increase the processing speed. However, there are additional considerations: the amount of time required by the token issued to read the image memory and to make a return trip to the uPD7281, and situations where there may be some systems where the overflow occurs depending on the number of uPD7281s involved.

Figure 2-3 (b)

A Flow Graph in Which an Overflow May Occur Depending on

the Time From When the Token is Issued to Read the Image

Memory Until the Token Returns to the uPD7281

## 2.1.6 Assembler Source Listing

```

1: ****

2: ;

3: ;      WORD BOUNDARY

4: ;

5: -----

6: ;

7: MODULE IPP    =     8          ;

8: ;

9: EQUATE H      =     512/16    ;

10: EQUATE V     =     512/16    ;

11: EQUATE L      =    1024/16    ;

12: ;

13: EQUATE HOST   =      0        ;

14: EQUATE READ   =      4        ;

15: EQUATE WRITE  =      5        ;

16: ;

17: EQUATE STARTS =      0        ;

18: EQUATE STARTD =     32        ;

19: ;

20: ****

21: ;

22: ;      INPUT-OUTPUT

23: ;

24: -----

25: ;

26: INPUT LSA0, LDA0, ARV8 AT 0    ;

27: ;

28: OUTPUT RDAT, WDAT, WADR, PEND  ;

29: ;

30: ****

31: ;

32: ;      LINK TABLE

33: ;

34: -----

35: ;

36: LINK MSA0, MSA0Q1, MSA00    =    GECB1  (LSA1, LSA0      ) ;

37: LINK LSA1,          =    QUE1   (MSA0Q1, IMRIQ1      ) ;

38: LINK IMRI, IMRIQ2, IMRIQ1    =    GECB2  (MSA1, MSA0      ) ;

39: LINK MSA1,          =    QUE2   (IMRIQ2, NOPQ2      ) ;

40: LINK RDAT,          =    IMRED  (IMRI1,          ) ;

41: LINK IMW0, IMW0QA,          =    CNTS   (ARV8          ) ;

42: LINK MDA0, MDA0Q3, MDA00    =    GECB3  (LDA1, LDA0      ) ;

43: LINK LDA1,          =    QUE3   (MDA0Q3, ARV9Q3      ) ;

44: LINK ARV9, ARV9Q4, ARV9Q3    =    GECB4  (MDA1, MDA0      ) ;

45: LINK MDA1,          =    QUE4   (ARV9Q4, NOPQ4      ) ;

46: LINK IMW1, IMW1QA,          =    CNTD   (ARV9          ) ;

47: LINK NOPQ2, NOPQ4,          =    QNOP   (IMW0QA, IMW1QA      ) ;

48: LINK WDAT, WADR,          =    QIMWRIT (IMW0, IMW1      ) ;

49: LINK OUTE,          =    QUES   (MDA00, MSA00      ) ;

50: LINK PEND,          =    OUT    (OUTE          ) ;

51: ;

```

```

52: ;*****;

53: ;

54: ;      FUNCTION TABLE

55: ;

56: ;

57: ;

58: FUNCTION IMRED = OUT1  (READ. 0) ;

59: FUNCTION QIMRT = OUT2  (WRITE. 20H. 0).QUEUE (Q6. 16) ;

60: FUNCTION OUT = OUT1  (HOST. 0) ;

61: FUNCTION GECB1 = COPYBK (1. 1), CNTGE (H. ) ;

62: FUNCTION GECB2 = COPYBK (16. L), CNTGE (V. ) ;

63: FUNCTION GECB3 = COPYBK (1. 1), CNTGE (H. ) ;

64: FUNCTION GECB4 = COPYBK (16. L), CNTGE (V. ) ;

65: FUNCTION QUE1 = QUEUE (Q1. 1) ;

66: FUNCTION QUE2 = QUEUE (Q2. 1) ;

67: FUNCTION QUE3 = QUEUE (Q3. 1) ;

68: FUNCTION QUE4 = QUEUE (Q4. 1) ;

69: FUNCTION QUES = QUEUE (Q5. 1) ;

70: FUNCTION CNTS = COUNT (16. ) ;

71: FUNCTION CNTD = COUNT (16. ) ;

72: FUNCTION QNOP = NOP (XY. ), QUEUE (QA. 1) ;

73: ;

74: ;*****;

75: ;

76: ;      DATA MEMORY

77: ;

78: ;

79: ;

80: MEMORY Q1 = AREA (1. ) ;

81: MEMORY Q2 = AREA (1. ) ;

82: MEMORY Q3 = AREA (1. ) ;

83: MEMORY Q4 = AREA (1. ) ;

84: MEMORY Q5 = AREA (1. ) ;

85: MEMORY Q6 = AREA (16. ) ;

86: MEMORY QA = AREA (1. ) ;

87: ;

88: ;*****;

89: ;

90: ;      START

91: ;

92: ;

93: ;

94: START

95: ;

96: DATA EXEC (IPP. LSA0. STARTS ) ;

97: DATA EXEC (IPP. LDA0. STARTD ) ;

98: ;

99: END

```

## Logical Operations

### 3.1 NOT (Single-Operand Operation)

#### 3.1.1 Processing Explained

The NOT operation is used in writing data, read from the image memory source area (SRC), to the destination area (DST) by performing bit inversions.

#### 3.1.2 Algorithm

First the SRC starting address (STARTS) and the DST starting address (STARTD) are received from the host computer as input parameters, as occurs in a word boundary transfer. Then, based on STARTS, data is read from SRC, block by block, in the vertical direction. The data is then NOT-operated, and the inverted data is written to the DST after being combined with its corresponding DST addresses (as in the case of a word boundary transfer).

Details are provided in Section 2.1, "Word Boundary Transfer."

#### 3.1.3 Parameters and Their Applicable Ranges

##### <Assembler-Coded Parameters>

L ... Number of image memory words in horizontal direction

H ... Number of source image area words in horizontal direction

V ... Number of destination image area blocks in vertical direction

##### <Start-up token-defined parameters>

STARTS ... Source image area (SRC) starting address

STARTD ... Destination image area (DST) starting address

The values that can be assigned to these parameters are as follows:

| Parameter | Applicable range | (Value set in the example program) |

|-----------|------------------|------------------------------------|

| L         | 0 - 65535        | (64)                               |

| H         | 1 - 256          | (32)                               |

| V         | 1 - 256          | (32)                               |

| STARTS    | 0 - 65535        | ( 0 ) *                            |

| STARTD    | 0 - 65535        | (32) *                             |

\* : Although STARTS and STARTD are variables (i.e., addresses), they are given default values since they are used in the assembler DATA statement. When the uPD7281 is started up, the starting addresses of the SRC and DST areas are input as execution tokens.

Since this program has no provision for bank switching, care should be exercised in setting the values for the parameters H and L.

#### <Initial Values>

Initial values used in this program are the same as those used in the word boundary transfer program. (See 2.1.3).

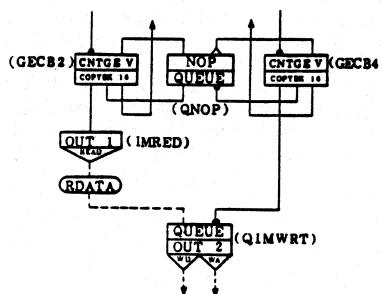

#### 3.1.4 Flow Graph Explained

The flow graph for the NOT operation, shown in Figure 3-1, represents the addition of SRC data NOT processing to the word boundary transfer flow graph given in Figure 2-1, except that the node for the COUNT instruction to ensure synchronization during a word boundary transfer has been removed. The method employed in the NOT operation for synchronizing SRC and DST processing is not an ideal one because there is a risk of an overflow occurring, depending on the reading time of SRC data. However, for the typical system configuration used in this example and for those cases where image memory access time is short, the synchronization method illustrated in the flow graph should be adequate and should yield improvements in processing speed.

Figure 3.1

A NOT (Single-Operand Operation) Flow Graph

### 3.1.5 Tips on Writing Flow Graphs

The SRC and DST processing must be synchronized for logical operations and transfer. In the absence of synchronization, some programs can run into a situation where an excess of data for either SRC processing or DST processing is created, resulting in a uPD7281 QUEUE overflow. The methods used in ensuring synchronization can vary, depending on the particular objective pursued and the way the flow graph is written. Any method used, however, must meet the following conditions:

- the work of the SRC token (the first input token) needs to be controlled; i.e., if the second of two tokens is not input after the first token is input, it should not be allowed to process SRC side operations independent of another side (DST, for example) resulting in an overflow on the image memory write QUEUE.

- when an external token is issued from the uPD7281, such as the image memory access token, you should take care to preclude errors due to the amount of access time required in the external circuits or due to the maximum number of tokens flowing around in the external components.

### 3.1.6 Assembler Source Listing

```

1: ;*****

2: ;

3: ; NOT OPERATION

4: ;

5: ;-----

6: ;

7: MODULE IPP      =      8          ;

8: ;

9: EQUATE L        =      64         ;

10: EQUATE H       =      32         ;

11: EQUATE V       =      32         ;

12: ;

13: EQUATE HOST    =      0          ;

14: EQUATE READ    =      4          ;

15: EQUATE WRITE   =      5          ;

16: ;

17: EQUATE START3  =      0          ;

18: EQUATE STARTD  =      32         ;

19: ;

20: ;*****

21: ;

22: ; INPUT-OUTPUT

23: ;

24: ;-----

25: INPUT  LSA8,  LDA8,  RDATA AT 8  ;

26: ;

27: OUTPUT RDAT,  WDAT,  WADR,  PEND  ;

28: ;

```

```

29: ;*****LINK TABLE*****

30: ;

31: ;      LINK TABLE

32: ;

33: ;-----

34: ;

35: LINK  MSA0, RSA0, RSA1 = FGEN1 (LSA1, LSA0 ) ;

36: LINK  IMR1, RSA2, RSA3 = FGEN2 (MSA1, MSA0 ) ;

37: LINK  LSA1,          = FQUE1 (RSA0, RSA3 ) ;

38: LINK  PEND,          = FOUTE (RSA1, RDA1 ) ;

39: LINK  RDAT,          = FIRRED (IRRI,          ) ;

40: LINK  MSA1, RDA1,    = FQNP  (RSA2, RDA2 ) ;

41: LINK  IMW0,          = FNOT  (RDATA,          ) ;

42: LINK  MDA1, RDA0, RDA1 = FGEN3 (LDA1, LDA0 ) ;

43: LINK  IMWI, RDA2, RDA3 = FGEN4 (MDA1, MDA0 ) ;

44: LINK  LDA1,          = FQUE2 (RDA0, RDA3 ) ;

45: LINK  WDAT, WADR,   = FIRWRIT (IMW0, IMWI ) ;

46: ;

47: ;*****FUNCTION TABLE*****

48: ;

49: ;      FUNCTION TABLE

50: ;

51: ;-----

52: ;

53: FUNCTION FIRRED = OUT1  (READ,  0) ;

54: FUNCTION FIRWRT = OUT2  (WRTIE, 20H, 0).QUEUE (QUEW, 16) ;

55: FUNCTION FOUTE = OUT1  (HOST,  0).QUEUE (QUEE,  1) ;

56: FUNCTION FGEN1 = COPYBK (1, 1), CNTGE (H, ) ;

57: FUNCTION FGEN2 = COPYBK (16, L), CNTGE (V, ) ;

58: FUNCTION FGEN3 = COPYBK (1, 1), CNTGE (H, ) ;

59: FUNCTION FGEN4 = COPYBK (16, L), CNTGE (V, ) ;

60: FUNCTION FQNP  = NOP   (XY, ),  QUEUE (QUEU, 1) ;

61: FUNCTION FNOT  = NOT   (X, ) ;

62: FUNCTION FQUE1 = QUEUE (QUE1, 1) ;

63: FUNCTION FQUE2 = QUEUE (QUE2, 1) ;

64: ;

65: ;*****DATA MEMORY*****

66: ;

67: ;      DATA MEMORY

68: ;

69: ;-----

70: ;

71: MEMORY QUE1 = AREA  (1, ) ;

72: MEMORY QUE2 = AREA  (1, ) ;

73: MEMORY QUEN = AREA  (1, ) ;

74: MEMORY QUEW = AREA  (16, ) ;

75: MEMORY QUEE = AREA  (1, ) ;

76: ;

77: ;*****START*****

78: ;

79: ;      START

80: ;

81: ;-----

82: ;

83: START

84: ;

85: DATA  EXEC  (IPP, LSA0, STARTS ) ;

86: DATA  EXEC  (IPP, LDA0, STARTD ) ;

87: ;

88: END

```

## 3.2 AND, OR, Exclusive OR (Double-Operand Operations)

### 3.2.1 Processing Explained

Given SRC1 and SRC2 as source image areas, these operations perform the specified operation (AND, OR, or Exclusive OR) between the data in these areas and outputs the resultant data to the destination image area. As in the case of the word boundary data transfer (discussed in 2.1), each of the areas, SRC1, SRC2, and DST, in this program are divided into word-aligned horizontal 16-dot (1 word) and vertical 16-dot (16 lines) rectangular areas (blocks) as units of data transfer. For the order of processing, refer to Section 2.1, "Word Boundary Transfer."

### 3.2.2 Algorithm

The starting read addresses S1ADR and S2ADR of source image areas SRC1 and SRC2, respectively, and the starting address DSTADR of destination image area DST are input from the host computer into the uPD7281 as part of a token. Then, one block of addresses are generated for each S1ADR and S2ADR, and the contents of the image memory at those addresses are read. Data in the two blocks just read are operated upon (AND, OR, or Exclusive OR) in conjunction with their corresponding data, resulting in the creation of DST data. The DST data are written out to the DST addresses generated on the basis of DSTADR.

### 3.2.3 Parameters and Their Applicable Ranges

#### Assembler-coded parameters:

L ... Number of image memory words in horizontal direction

H ... Number of source image area words in horizontal direction

V ... Number of source image area blocks in vertical direction

#### Start-up token-defined parameters:

S1ADR ... First operand source image area (SRC1) starting address

S2ADR ... Second operand source image area (SRC2) starting address

DSTADR .. Destination image area (DST) starting address

The allowable values of these parameters are as follows:

| Parameter | Applicable range | (Value set in the example program) |

|-----------|------------------|------------------------------------|

| L         | 0 - 65535        | (64)                               |

| H         | 1 - 256          | (16)                               |

| V         | 1 - 256          | (16)                               |

| S1ADR     | 0 - 65535        | ( 0 )*                             |

| S2ADR     | 0 - 65535        | (4000H)*                           |

| DSTADR    | 0 - 65535        | ( 0 )*                             |

\* : Although STARTS and STARTD are variables (i.e., addresses), they are given default values since they are used in the assembler DATA statement. When the uPD7281 is started up, the starting addresses of the SRC and DST areas are input as execution tokens.

Since no provision is made in this program for switching banks, you should exercise care in setting values for parameters H and V.

#### <Initial Values>

Most of the initial values used in this program are the same as those used in the word boundary transfer program, except that initial values need to be assigned to the two SRC addresses.

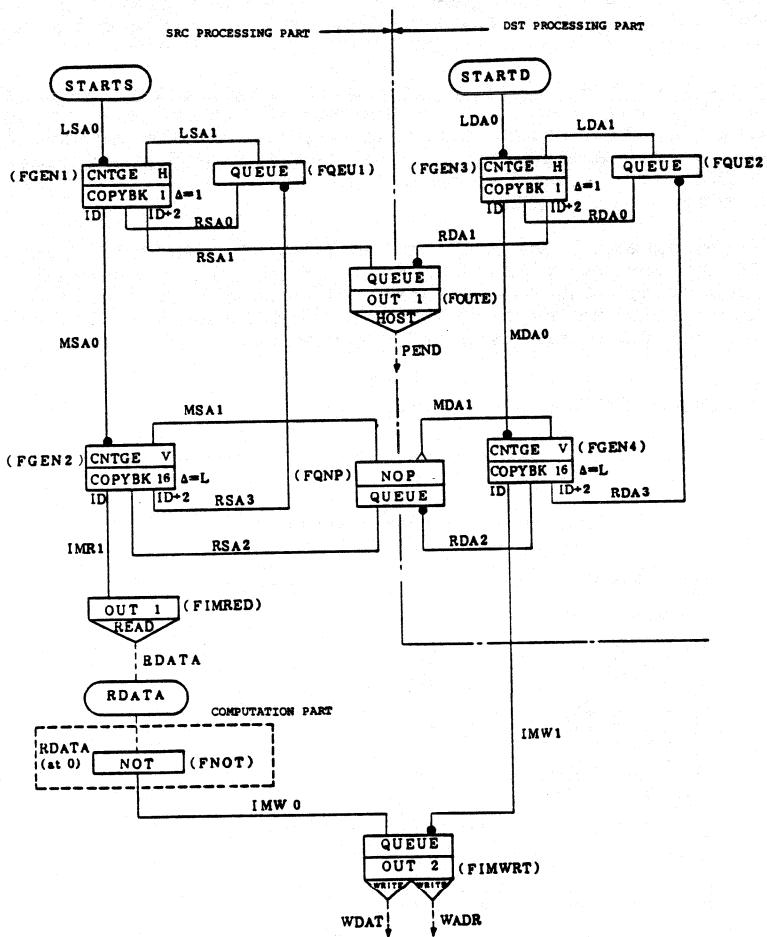

#### 3.2.4 Flow Graph Explained

This program illustrates the use of the OR operation. To use AND or Exclusive OR, change "OR" to "AND" or "XOR" (XOR is the instruction code for the Exclusive OR operation) in the FQOR node in Figure 3-2.

#### <Explanation of Nodes>

- FGEN1/FGEN3 : Creates H blocks of horizontal starting addresses on the basis of the starting addresses S1ADR/S2ADR for SRC1/SRC2.

- FGEN2/FGEN4 : Creates V blocks of in-block addresses on the basis of addresses sent from FGEN1/FGEN3.

- FIMRD1/FIMRD2 : Reads the contents of SRC1/SRC2 on the basis of addresses created in FGEN2/FGEN4.

- FQOR : Creates DST data by performing the OR

between the data read in FIMRD1 and FIMRD2.

FGEN5 : Creates H blocks of DST horizontal starting addresses on the basis of the DST starting address DSTADR

FGEN6 : Creates V blocks of in-block DST addresses on the basis of addresses generated in FGEN5.

FIMWRT : Writes DST data created in FQOR to the DST addresses generated in FGEN6.

FQUE1/FQUE2/FQUE3 : Synchronizes the actions of FGEN1/FGEN3/FGEN5 so that they make V blocks worth of addresses at a time.

FQNP1/FQNP2/FQNP3 : Synchronizes the actions of SRC and DST processing whenever one block of addresses are created in FGEN2, FGEN4, or FGEN6.

Figure 3-2

A Double-Operand Operation Flow Graph (OR)

### 3.2.5 Tips on Writing Flow Graphs

This program is basically the same as the word boundary transfer program in 2.1, except for minor differences that exist in the synchronization method because of the need to access three areas.

### 3.2.6 Assembler Source Listing

```

1: ****

2: :

3: :      LOGICAL OPERATION

4: :

5: -----

6: :

7: MODULE IPP      =     8      :

8: :

9: EQUATE L        =     64     :

10: EQUATE H       =     16     :

11: EQUATE V       =     16     :

12: :

13: EQUATE HOST    =     0      :

14: EQUATE READ    =     4      :

15: EQUATE WRITE   =     5      :

16: :

17: EQUATE S1ADR   =     0      :

18: EQUATE S2ADR   = 256*L    :

19: EQUATE DSTADR =     0      :

20: :

21: :

22: ****

23: :

24: :      INPUT-OUTPUT

25: :

26: -----

27: :

28: INPUT  SRCH11, SRCH21, DSTH1      :

29: INPUT  QOR0 AT 0      :

30: INPUT  QOR1 AT 1      :

31: :

32: OUTPUT RDAT1, RDAT2, WDAT, WADR, PEND  :

33: :

34: ****

35: :

36: :      LINK TABLE

37: :

38: -----

39: :

40: LINK  SRCV11, SRCR1, SRCR2  =  FGEN1  (SRCH12,SRCH11  )

41: LINK  OTR01, SRCR3, SRCR4  =  FGEN2  (SRCV12,SRCV11  )

42: LINK  SRCH12      =  FQUE1  (SRCR1, SRCR4  )

43: LINK  OUTH       =  FVAN   (          ,SRCR2  )

44: LINK  RDAT1      =  FIRRD1 (OTRD1  )

45: LINK  SRCV12, QNOP3  =  FQNP2  (SRCR3, QNOP1  )

46: LINK  SRCV21, SRCR5, SRCR6  =  FGEN3  (SRCH22,SRCH21  )

47: LINK  OTR02, SRCR7, SRCR8  =  FGEN4  (SRCV22,SRCV21  )

48: LINK  SRCH22      =  FQUE2  (SRCR5, SRCR8  )

49: LINK  OUTH       =  FVAN   (          ,SRCR6  )

50: LINK  RDAT2      =  FIRRD2 (OTRD2  )

51: LINK  QNOP1, QNOP2  =  FQNP1  (SRCR7, DSTR3  )

52: LINK  OTWT0      =  FQOR   (QOR0, QOR1  )

53: LINK  SRCV22, DSTV2  =  FQNP3  (QNOP3, QNOP2  )

54: LINK  DSTV1, DSTR1, DSTR2  =  FGEN5  (DSTH2, DSTH1  )

55: LINK  OTWT1, DSTR3, DSTR4  =  FGEN6  (DSTV2, DSTV1  )

56: LINK  DSTH2      =  FQUE3  (DSTR1, DSTR4  )

57: LINK  OUTH       =  FVAN   (          ,DSTR2  )

58: LINK  WDAT, WADR      =  FIMURT (OTWT0, OTWT1  )

59: LINK  PEND      =  FOUTE  (OUTH  )

60: :

```

```

61: ;-----

62: ;

63: ;      FUNCTION TABLE

64: ;

65: ;-----

66: ;

67: FUNCTION  FIRRD1 = OUT1  (READ,  0)  ;

68: FUNCTION  FIRRD2 = OUT1  (READ,  1)  ;

69: FUNCTION  FIRWRT = OUT2  (WRITIE, 20H, 0).QUEUE  (QUEW, 16)  ;

70: FUNCTION  FOUTE = OUT1  (HOST,  0)  ;

71: FUNCTION  FGEN1 = COPYBK (1,  1),  CNTGE (H  )  ;

72: FUNCTION  FGEN2 = COPYBK (16, L),  CNTGE (V  )  ;

73: FUNCTION  FGEN3 = COPYBK (1,  1),  CNTGE (H  )  ;

74: FUNCTION  FGEN4 = COPYBK (16, L),  CNTGE (V  )  ;

75: FUNCTION  FGEN5 = COPYBK (1,  1),  CNTGE (H  )  ;

76: FUNCTION  FGEN6 = COPYBK (16, L),  CNTGE (V  )  ;

77: FUNCTION  FQOR = OR (X  ),  QUEUE (QUEOR, 16)  ;

78: FUNCTION  FQNP1 = NOP (XY  ),  QUEUE (QUE1, 1)  ;

79: FUNCTION  FQNP2 = NOP (XY  ),  QUEUE (QUE2, 1)  ;

80: FUNCTION  FQNP3 = NOP (XY  ),  QUEUE (QUE3, 1)  ;

81: FUNCTION  FQUE1 = QUEUE (QUE1, 1)  ;

82: FUNCTION  FQUE2 = QUEUE (QUE2, 1)  ;

83: FUNCTION  FQUE3 = QUEUE (QUE3, 1)  ;

84: FUNCTION  FVAN = WRCYCS (WTVAN, 3)  ;

85: ;

86: ;-----

87: ;

88: ;      DATA MEMORY

89: ;

90: ;-----

91: ;

92: MEMORY  QUE1 = AREA (1  )  ;

93: MEMORY  QUE2 = AREA (1  )  ;

94: MEMORY  QUE3 = AREA (1  )  ;

95: MEMORY  QUE1 = AREA (1  )  ;

96: MEMORY  QUE2 = AREA (1  )  ;

97: MEMORY  QUE3 = AREA (1  )  ;

98: MEMORY  QUEOR = AREA (16  )  ;

99: MEMORY  QUEW = AREA (16  )  ;

100: MEMORY  WTVAN = AREA (3  )  ;

101: ;

102: ;-----

103: ;

104: ;      START

105: ;

106: ;-----

107: ;

108: START

109: ;

110: DATA  EXEC  (IPP,  SRCH11,  SIADR  )  ;

111: DATA  EXEC  (IPP,  SRCH21,  S2ADR  )  ;

112: DATA  EXEC  (IPP,  DSTH1,  DSTADR  )  ;

113: ;

114: END

```

## Chapter 4

### Enlargement and Shrinking

#### 4.1 Simple One-Half Shrinking

##### 4.1.1 Processing Explained

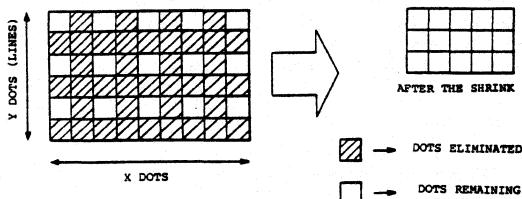

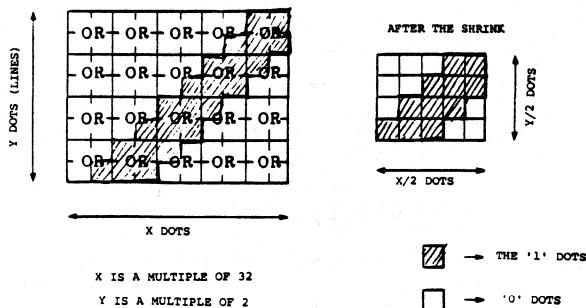

Simple one-half shrinking means a shrinking by simple elimination of source image area (SRC) data, as shown in the figure below.

Figure 4-1

Simple One-Half Shrinking

##### 4.1.2 Algorithm

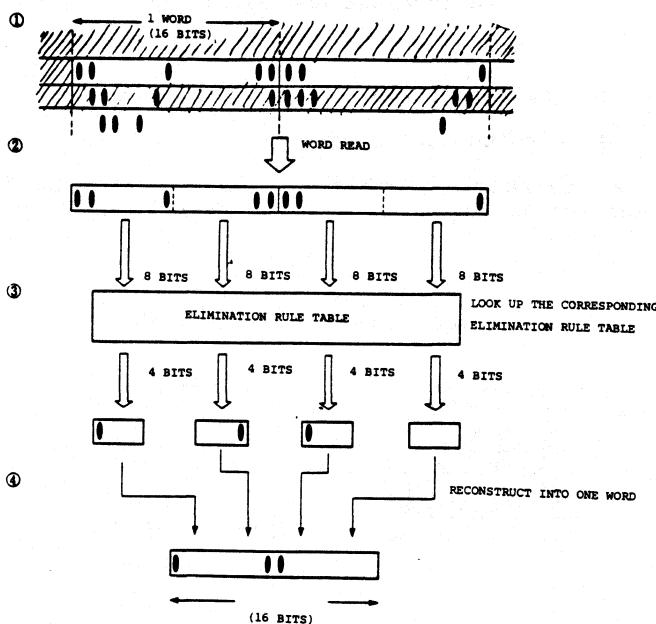

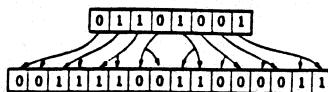

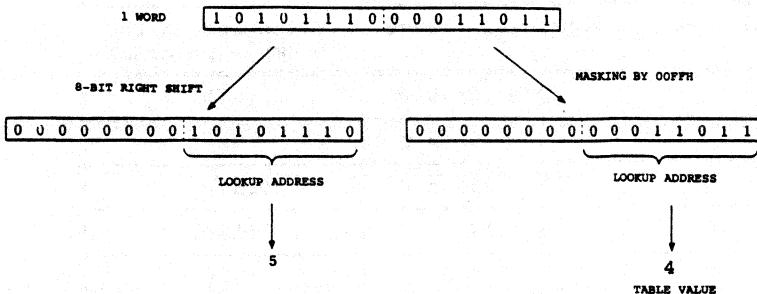

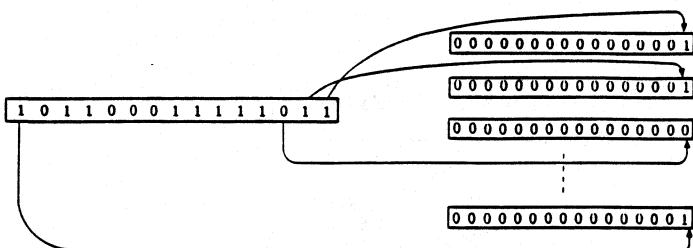

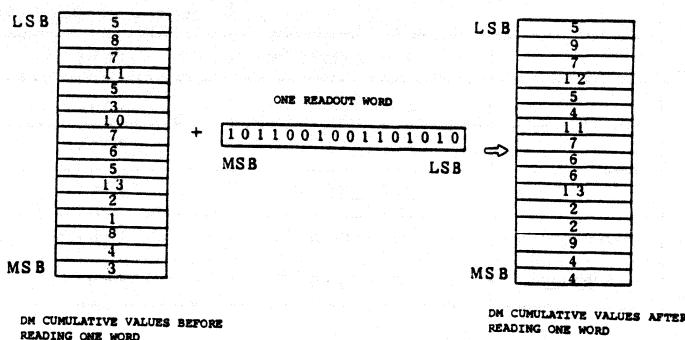

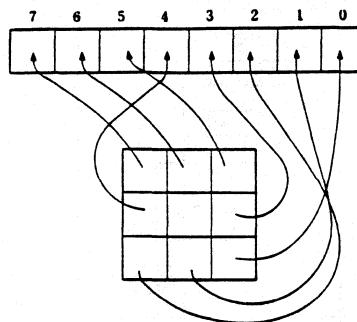

Since all that is involved is a simple elimination, data are read vertically by skipping every other line. Horizontally, 16-bit data that are read are subjected to elimination by looking up an elimination rule table. To avoid the problem of handling a large 16-bit table, the data are divided into high-order and low-order 8-bit segments. A 256-word (8-bit address) elimination rule table is provided for each of these segments. The use of the 256-word table results in 4-bit data. Four pieces of such 4-bit data are written to the destination image area (DST) as one word (See Figure 4-2).

Figure 4-2

Algorithm for Simple One-Half Shrinking

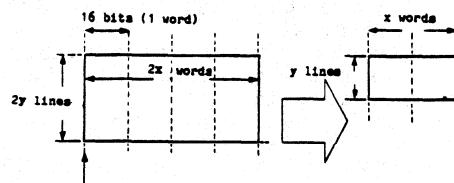

#### 4.1.3 Parameters and Their Applicable Ranges

##### <Assembler-coded parameters>

L ... Number of image memory words in horizontal direction

H ... Number of destination image area (DST) words in horizontal direction

M ... Number of destination image area (DST) lines in vertical direction

##### <Start-up token-defined parameters>

STARTS ... Source image area (SRC) starting address

STARTD ... Destination image area (DST) starting address

The allowable values of these parameters are indicated in the table below.

| Parameter | Applicable range | (Value set in the example program) |

|-----------|------------------|------------------------------------|

| L         | 0 - 32767        | (64)                               |

| H         | 1 - 16           | (16)                               |

| M         | 1 - 256          | (256)                              |

| STARTS    | 0 - 65535        | (0)*                               |

| STARTD    | 0 - 65535        | (32)*                              |

\* : Although STARTS and STARTD are variables (i.e., addresses), they are given default values since they are used in the assembler DATA statement. When the uPD7281 is started up, the starting addresses of the SRC and DST areas are input as execution tokens.

Since no provision is made in this program for switching banks, you should exercise care in setting the values of parameters H and M. The maximum allowable values of these parameters in this program are H=16 and M=256; in other words, the maximum size of a destination image that can be reduced is 16 words horizontally and 256 lines vertically.

#### <Initial Values>

In setting initial values, the horizontal size of a SRC to be shrunk is defined in an even number of words, and the vertical size is defined in an even number of lines. Since the process involved is a simple one-half shrinking, once the size on the SRC side is determined, the size of the reduced image on the DST side is determined automatically.

The units in the horizontal direction must always be aligned with word boundaries.

Notice that, because DSTs are written word by word, the horizontal and vertical SRC definition numbers must always be multiples of 2.

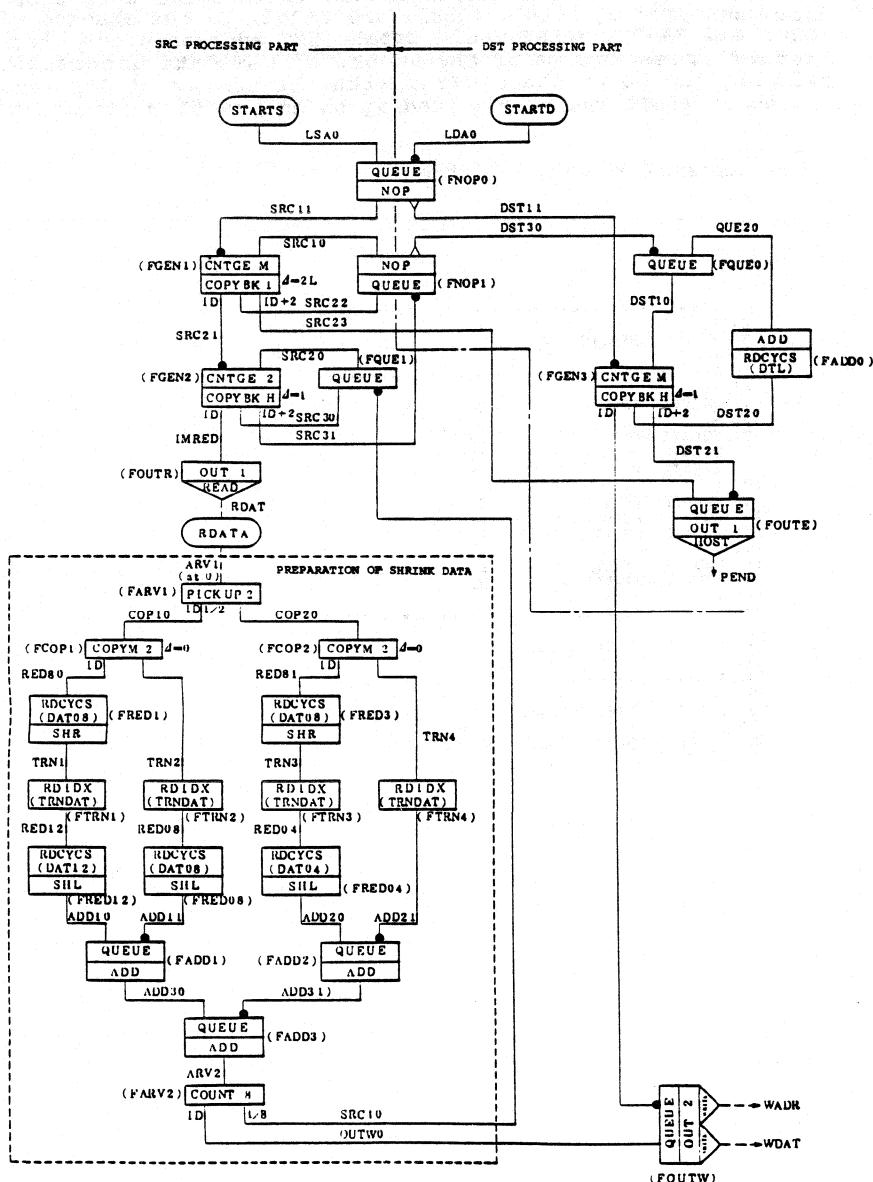

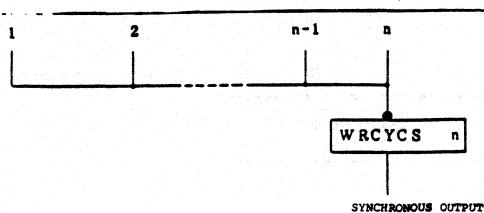

#### 4.1.4 Flow Graph Explained

This program consists of a SRC processing part (which reads every other line of the SRC data and creates shrunken data), and a DST part (which creates addresses necessary for writing the shrunk data). Shrunk data is generated on the basis of words of data at two contiguous addresses on the SRC side (the first word corresponds with the high-order 8 bits, and the second word with the low-order 8 bits). The SRC part receives from the host computer an SRC address which indicates the starting address of the shrinking processing, reads the SRC data horizontally every other line starting with the given SRC address, and separates them into high-order 8-bit and low-order 8-bit segments.

Each of the high-order 8-bit and low-order 8-bit segments is used as an address for a look-up table to generate high-order 4-bit and low-order 4-bit data generations. Four pieces of the 4-bit data thus created by two SRC data are placed in their respective bit positions to constitute DST (shrunk) data. That is, one DST data is created by two SRC data.

The DST processing part receives the starting address for writing the shrunk data from the host computer and creates write addresses on the basis of this address.

#### <Explanation of Nodes>

- FNOP0 : Synchronizes the actions of start-up tokens received from the host computer and indicating SRC (STARTS) and DST (STARTD) addresses, and sends them to the SRC and DST processing parts.

- FGEN1 : Creates line starting addresses for every other line in order to read SRC data. (Creates vertical addresses for every other line on the basis of the SRC address sent from FNOP0.)

- FGEN2 : Creates one line of SRC data addresses in two passes, on the basis of addresses generated in FGEN1.

- FOUTR : Reads the contents of SRC addresses generated in FGEN2.

- FARV1 : Sends SRC data read in FOUTR alternately (high-order and low-order 8 bits) to the DST data generation node.

- FCOP1/FCOP2 : In the generation of high-order and low-order 8-bit data from the 16-bit data separated by FARV1, makes two copies of the data so that the high-order 4 bits of DST

data can be created from the high-order 8 bits of 16-bit SRC data, and the low-order 4 bits of DST data from the low-order 8 bits of the SRC data.

**FRED1/FRED3** : Performs a right 8-bit shift to enable FTRN1/FTRN3 to look up the elimination rule data table on the basis of the high-order 8 bits of 16-bit SRC data.

**FTRN1/FTRN3** : Looks up the elimination rule data table on the basis of the high-order 8 bits of 16-bit SRC data, and creates high-order 4-bit data for the high-order and low-order 8-bit DST data.

**FTRN2/FTRN4** : Looks up the elimination rule table on the basis of the low-order 8 bits of a second copy of SRC data made in FCOP1/FCOP2, creates 4-bit elimination data for the low-order 8 bits, and assigns them as low-order 4-bit portions of the high-order and low-order 8-bit DST data. (4-bit data created in FTRN4 becomes the low-order 4-bit portion of the low-order 8-bit portion of the DST data.)

**FRED12/FRED08** : Performs a 12/8 left shift on the 4-bit data created in FTRN1/FTRN2 and makes them into the high-order and low-order 4 bits of the high-order 8-bit DST data.

**FRED04** : Performs a 4-bit left shift on the 4-bit data created in FTRN3 and makes it into high-order 4 bits of the low-order 8 bits of DST data.

**FADD1/FADD2** : Adds the data created in FRED12/FRED04 and FRED08/FTRN4 together and creates high-order and low-order 8 bits of DST data.

**FADD3** : Adds the data created in FADD1 and FADD2 together and makes them into DST data.

**FARV2** : To enable FGEN2 to create SRC readout addresses each time 8 DST data are generated, notifies FQUEL that the eighth data has been copied and that 8 DST data have been generated.

**FGEN3** : Creates M lines of addresses for H horizontal words starting from the DST starting address STARTD sent from FNOP0.

**FOUTW** : Writes the reduced data generated by the SRC processing into the DST address created in FGEN3.

**FADD0** : Upon completion of the generation of H words of horizontal addresses by FGEN3, modifies the addresses sent by FGEN3 in order to create addresses for the next line.

**FNOP1** : Synchronizes the actions of FGEN1 and FGEN2 so that FGEN1 can create the starting address of a line each time FGEN2 generates addresses for one line of SRC data.

**FQUE1** : Synchronizes the actions of FGEN2 and FARV2 so that SRC addresses will be created each time 8 DST data are generated.

**FQUE2** : Synchronizes the actions of the SRC and DST processing parts so that the DST processing can create one line of addresses each time the SRC processing part generates one line of DST data.

Figure 4-3

A Flow Graph for Simple One-Half Shrinking

#### 4.1.5 Tips on Writing Flow Graphs

In this program 16 SRC addresses are created for each 8 DST data generated by FGEN2, FQUE1, and FARV2. In the absence of FQUE1 and FARV2, FGEN2 would create SRC addresses one after another irrespective of the number of DST data generated, filling the GQ of the uPD7281 with the tokens of SRC data copied in FROP1 and FCOP2, leading to an overflow situation.

#### 4.1.6 Assembler Source Listing

```

1: ****

2: :

3: :      SHRINK 1/2

4: :

5: -----

6: :

7: MODULE IPP    =     8      ;

8: :

9: EQUATE L      =     64     ;

10: EQUATE M     =    256     ;

11: EQUATE H     =     16     ;

12: :

13: EQUATE HOST   =     0      ;

14: EQUATE READ   =     4      ;

15: EQUATE WRITE  =     5      ;

16: :

17: EQUATE STARTS =     0      ;

18: EQUATE STARTD =    32     ;

19: :

20: ****

21: :

22: :      INPUT-OUTPUT

23: :

24: -----

25: :

26: INPUT  LSA0,  LDA0,  ARVI AT 0      ;

27: :

28: OUTPUT  RDAT,  WDAT,  WADR,  PEND    ;

29: :

```

```

30: ****

31: :

32: :      LINK TABLE

33: :

34: :

35: :

36: LINK  SRC11, DST11      =  FNOP0  (LSA0, LDA0  )

37: LINK  SRC21, SRC22,  SRC23  =  FGEN1  (SRC10, SRC11  )

38: LINK  OUTW1, DST20, DST21  =  FGEN3  (DST10, DST11  )

39: LINK  IMRED, SRC30, SRC31  =  FGEN2  (SRC20, SRC21  )

40: LINK  SRC10, DST30      =  FNOP1  (SRC22, SRC31  )

41: LINK  PEND              =  FOUTE  (SRC23, DST21  )

42: LINK  RDAT              =  FOUTR  (IMRED   )

43: LINK  SRC20              =  FQUE1  (SRC30, SRC40  )

44: LINK  COP10, COP20      =  FARV1  (ARV1   )

45: LINK  RED80, TRN2        =  FCOP1  (COP10   )

46: LINK  TRN1               =  FRED1  (RED80   )

47: LINK  RED12               =  FTRN1  (TRN1   )

48: LINK  ADD10               =  FRED12  (RED12   )

49: LINK  RED08               =  FTRN2  (TRN2   )

50: LINK  ADD11               =  FRED08  (RED08   )

51: LINK  ADD30               =  FADD1  (ADD10, ADD11  )

52: LINK  RED81, TRN4        =  FCOP2  (COP20   )

53: LINK  TRN3               =  FRED3  (RED81   )

54: LINK  RED04               =  FTRN3  (TRN3   )

55: LINK  ADD20               =  FRED04  (RED04   )

56: LINK  ADD21               =  FTRN4  (TRN4   )

57: LINK  ADD31               =  FADD2  (ADD20, ADD21  )

58: LINK  ARV2               =  FADD3  (ADD30, ADD31  )

59: LINK  OUTW0, SRC40      =  FARV2  (ARV2   )

60: LINK  WDAT, WADR        =  FOUTW  (OUTW0, OUTW1  )

61: LINK  QUE20              =  FADD0  (DST20   )

62: LINK  DST10              =  FQUE0  (QUE20, DST30  )

63: :

64: ****

65: :

66: :      FUNCTION TABLE

67: :

68: :

69: :

70: FUNCTION  FOUTR  =  OUT1  (READ, 0)

71: FUNCTION  FOUTW  =  OUT2  (WRTIE, 20H, 0), QUEUE (QUEW, 16)

72: FUNCTION  FOUTE  =  OUT1  (HOST, 0),   QUEUE (QUEE, 1)

73: FUNCTION  FGEN1  =  COPYBK (1, 2*L),  CNTGE (M   )

74: FUNCTION  FGEN2  =  COPYBK (H, 1),    CNTGE (2   )

75: FUNCTION  FGEN3  =  COPYBK (H, 1),    CNTGE (M   )

76: FUNCTION  FARV1  =  PICKUP (2   )

77: FUNCTION  FARV2  =  COUNT (8   )

78: FUNCTION  FCOP1  =  COPYM (2, 0)

79: FUNCTION  FCOP2  =  COPYM (2, 0)

80: FUNCTION  FRED1  =  SHR  (X   ),   RDCYCS (DAT08, 1)

81: FUNCTION  FRED3  =  SHR  (X   ),   RDCYCS (DAT08, 1)

82: FUNCTION  FRED12  =  SHL  (X   ),   RDCYCS (DAT12, 1)

83: FUNCTION  FRED08  =  SHL  (X   ),   RDCYCS (DAT08, 1)

84: FUNCTION  FRED04  =  SHL  (X   ),   RDCYCS (DAT04, 1)

85: FUNCTION  FTRN1  =  RDIDX (TRNDAT  )

86: FUNCTION  FTRN2  =  RDIDX (TRNDAT  )

87: FUNCTION  FTRN3  =  RDIDX (TRNDAT  )

88: FUNCTION  FTRN4  =  RDIDX (TRNDAT  )

89: FUNCTION  FADD0  =  ADD  (X   ),   RDCYCS (DTL, 1)

90: FUNCTION  FADD1  =  ADD  (X   ),   QUEUE (QUE4, 8)

91: FUNCTION  FADD2  =  ADD  (X   ),   QUEUE (QUE5, 8)

92: FUNCTION  FADD3  =  ADD  (X   ),   QUEUE (QUE6, 8)

93: FUNCTION  FNOP0  =  NOP  (XY   ),   QUEUE (QUE2, 1)

94: FUNCTION  FNOP1  =  NOP  (XY   ),   QUEUE (QUE3, 1)

95: FUNCTION  FQUE0  =  QUEUE (QUE0, 1)

96: FUNCTION  FQUE1  =  QUEUE (QUE1, 1)

97: :

```

```

98: ****

99: ;

100: ;      DATA MEMORY

101: ;

102: ;

103: ;

104: MEMORY  QUE0  =  AREA  (1      )  ;

105: MEMORY  QUE1  =  AREA  (1      )  ;

106: MEMORY  QUE2  =  AREA  (1      )  ;

107: MEMORY  QUE3  =  AREA  (1      )  ;

108: MEMORY  QUE4  =  AREA  (8      )  ;

109: MEMORY  QUES  =  AREA  (8      )  ;

110: MEMORY  QUE6  =  AREA  (8      )  ;

111: MEMORY  QUEW  =  AREA  (16     )  ;

112: MEMORY  QUEE  =  AREA  (1      )  ;

113: MEMORY  DAT04 =  4      ;      ;

114: MEMORY  DAT08 =  8      ;      ;

115: MEMORY  DAT12 =  12     ;      ;

116: MEMORY  DTL   =  L-16    ;      ;

117: MEMORY  TRNDAT =  0, 1, 0, 1, 2, 3, 2, 3, 0, 1, 0, 1, 2, 3, 2, 3,

118:           4, 5, 4, 5, 6, 7, 6, 7, 4, 5, 4, 5, 6, 7, 6, 7,

119:           0, 1, 0, 1, 2, 3, 2, 3, 0, 1, 0, 1, 2, 3, 2, 3,

120:           4, 5, 4, 5, 6, 7, 6, 7, 4, 5, 4, 5, 6, 7, 6, 7,

121:           8, 9, 8, 9, 10, 11, 10, 11, 8, 9, 8, 9, 10, 11, 10, 11,

122:           12, 13, 12, 13, 14, 15, 14, 15, 12, 13, 12, 13, 14, 15, 14, 15,

123:           8, 9, 8, 9, 10, 11, 10, 11, 8, 9, 8, 9, 10, 11, 10, 11,

124:           12, 13, 12, 13, 14, 15, 14, 15, 12, 13, 12, 13, 14, 15, 14, 15,

125:           0, 1, 0, 1, 2, 3, 2, 3, 0, 1, 0, 1, 2, 3, 2, 3,

126:           4, 5, 4, 5, 6, 7, 6, 7, 4, 5, 4, 5, 6, 7, 6, 7,

127:           0, 1, 0, 1, 2, 3, 2, 3, 0, 1, 0, 1, 2, 3, 2, 3,

128:           4, 5, 4, 5, 6, 7, 6, 7, 4, 5, 4, 5, 6, 7, 6, 7,

129:           8, 9, 8, 9, 10, 11, 10, 11, 8, 9, 8, 9, 10, 11, 10, 11,

130:           12, 13, 12, 13, 14, 15, 14, 15, 12, 13, 12, 13, 14, 15, 14, 15,

131:           8, 9, 8, 9, 10, 11, 10, 11, 8, 9, 8, 9, 10, 11, 10, 11,

132:           12, 13, 12, 13, 14, 15, 14, 15, 12, 13, 12, 13, 14, 15, 14, 15 ;

133: ;

134: ****

135: ;

136: ;      START

137: ;

138: ;

139: ;

140: START ;      ;

141: ;

142: DATA   EXEC  (IPP,   LSA0,   STARTS )  ;

143: DATA   EXEC  (IPP,   LDA0,   STARTD )  ;

144: ;

145: END   ;      ;

```

## 4.2 Four-Point OR One-Half Shrinking

### 4.2.1 Processing Explained

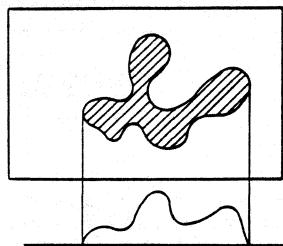

In the four-point OR one-half shrinking method, the OR operation is performed on four adjacent points in a given source image area (SRC), and the resulting single dot is made into destination image (DST) data, as shown in Figure 4-4.

**Figure 4-4**

An Example of a Four-Point OR One-Half Shrinking

(450 straight line)

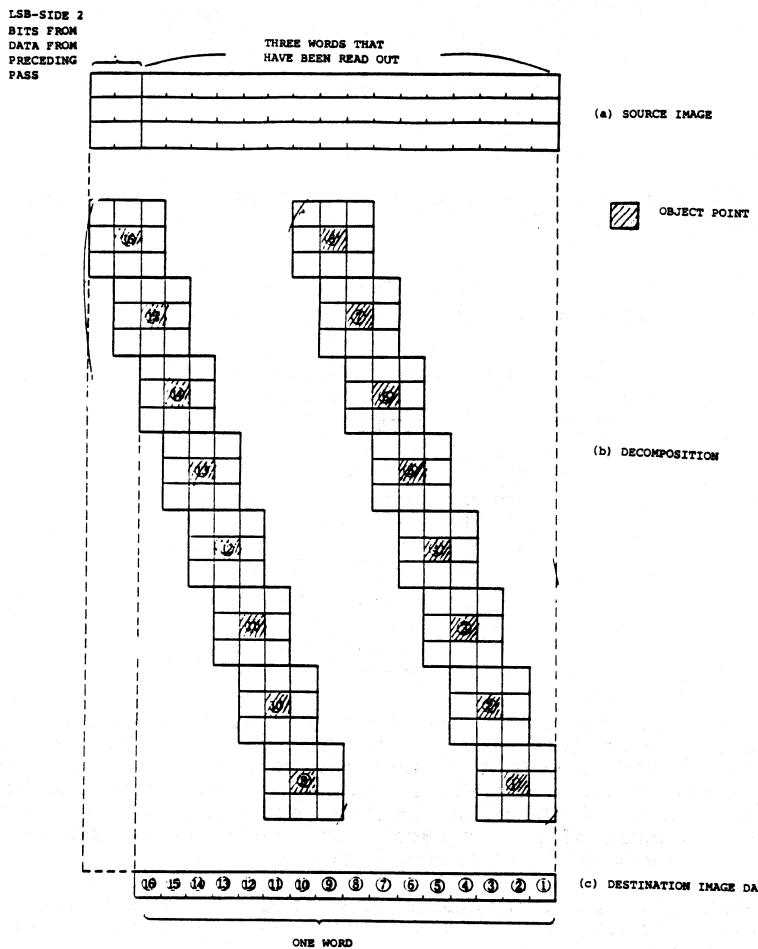

### 4.2.2 Algorithm

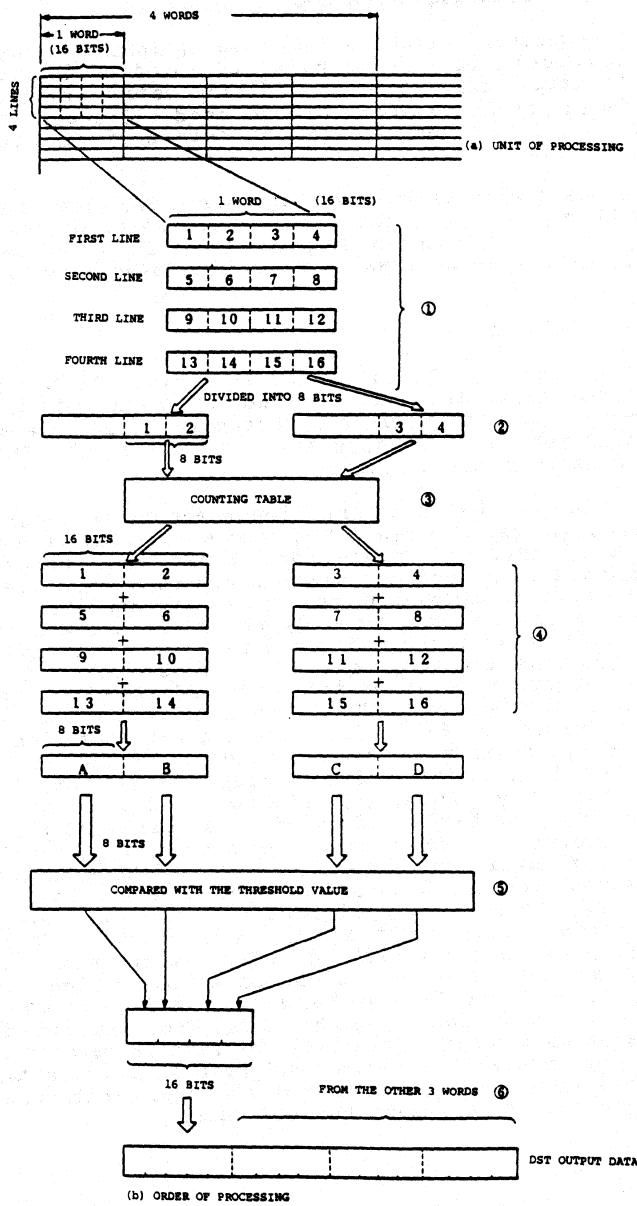

Since the four-point OR one-half shrinking method involves performing the OR operation on four adjacent points, the data that would not have been useful under the Simple One-Half Reduction method of Section 4.1 is required here. As shown in Figure 4-5, in this program a given line and the line following it are read one after another from the SRC in word units, the two lines are ORed, and the results are used to look up the OR table.

**Figure 4.5**

**Algorithm for the Four-Point OR One-Half Shrinking Method**

#### 4.2.3 Parameters and Their Applicable Ranges

##### <Assembler-coded parameters>

**L** ... Number of image memory words in horizontal direction

**H** ... Number of destination image area (DST) words in horizontal direction

**M** ... Number of destination image area (DST) lines in vertical direction

##### <Start-up token-defined parameters>

**STARTS** ... Source image area (SRC) starting address

**STARTD** ... Destination image area (DST) starting address

The allowable values of these parameters are indicated in the table below.

| Parameter | Applicable range | (Value set in the example program) |

|-----------|------------------|------------------------------------|

| L         | 0 - 32767        | (64)                               |

| H         | 1 - 16           | (16)                               |

| M         | 1 - 256          | (256)                              |

| STARTS    | 0 - 65535        | ( 0 )*                             |

| STARTD    | 0 - 65535        | (32)*                              |

\* : Although STARTS and STARTD are variables (i.e., addresses), they are given default values since they are used in the assembler DATA statement. When the uPD7281 is started up, the starting addresses of the SRC and DST areas are input as execution tokens.

Since no provision is made in this program for switching banks, you should exercise care in setting the values of the parameters H and M. Maximum values that can be assigned to these parameters are H=16 and M=256; therefore, the maximum size destination image that can be shrunk by this program is 16 horizontal words and 256 vertical lines.

#### <Initial Values>

The initial values used in this program are basically the same as those employed in the Simple One-Half Shrinking Method described in Section 4.1, except that the lines that would be skipped in a simple one-half shrinking need to be read out from the SRC and initial values must be provided for the processing involved in the creation of these read addresses.

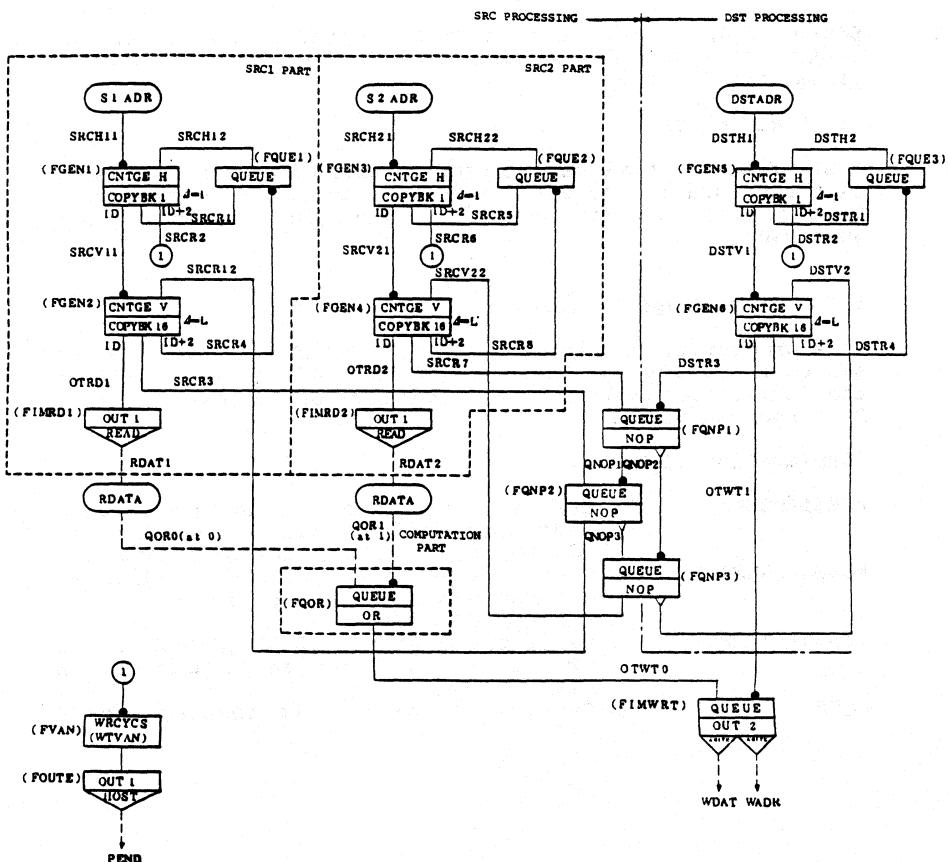

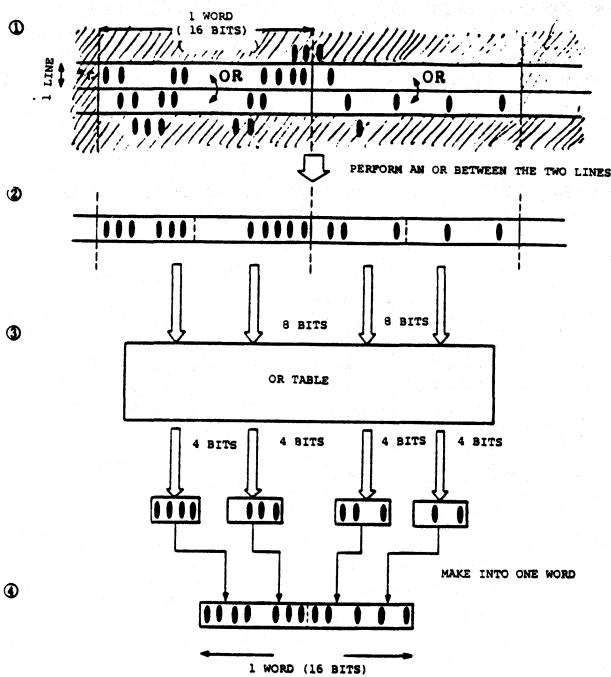

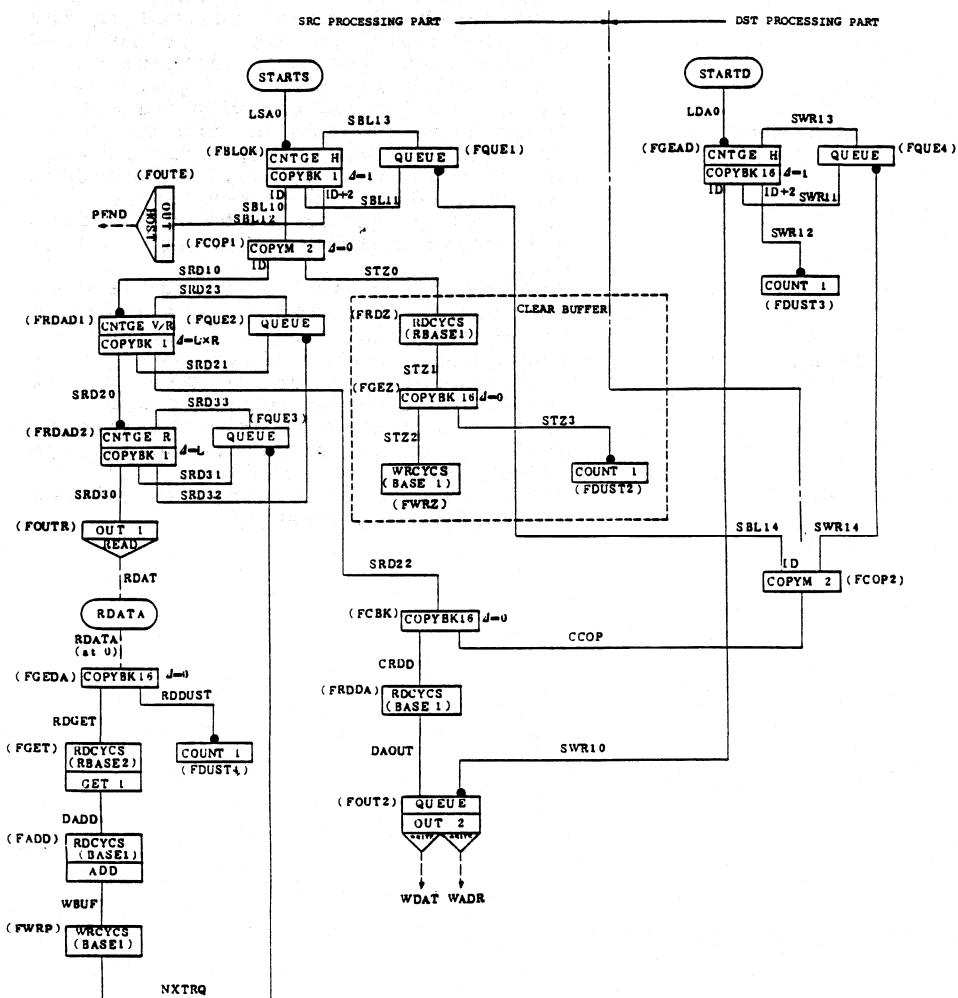

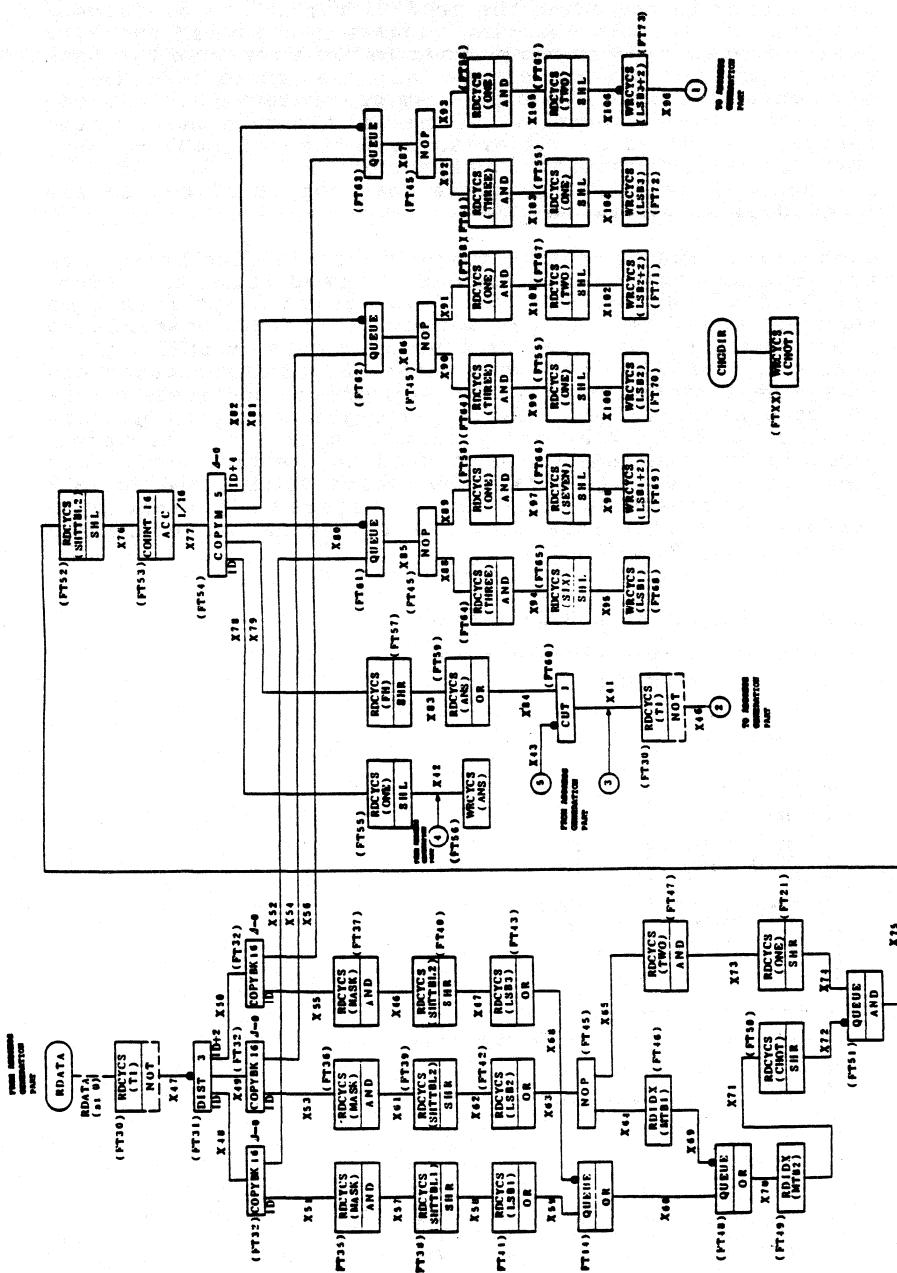

#### 4.2.4 Flow Graph Explained

The four-point OR one-half shrinking method differs from the simple one-half shrinking method of Section 4.1 in the following respects:

- (1) With an SRC starting address (STARTS) entered, the processing branches into two parts: A, which handles the creation of SRC addresses for every other line, as done during the simple one-half shrinking; and A', which creates those addresses which are not created by A above.

- (2) These two processing steps are performed in parallel, each reading the SRC data.

- (3) The two types of SRC data read in step (2) undergo an

OR operation, followed by a table lookup and the generation of shrunk data. The table used in this step is different from the one employed in the simple one-half shrinking method.

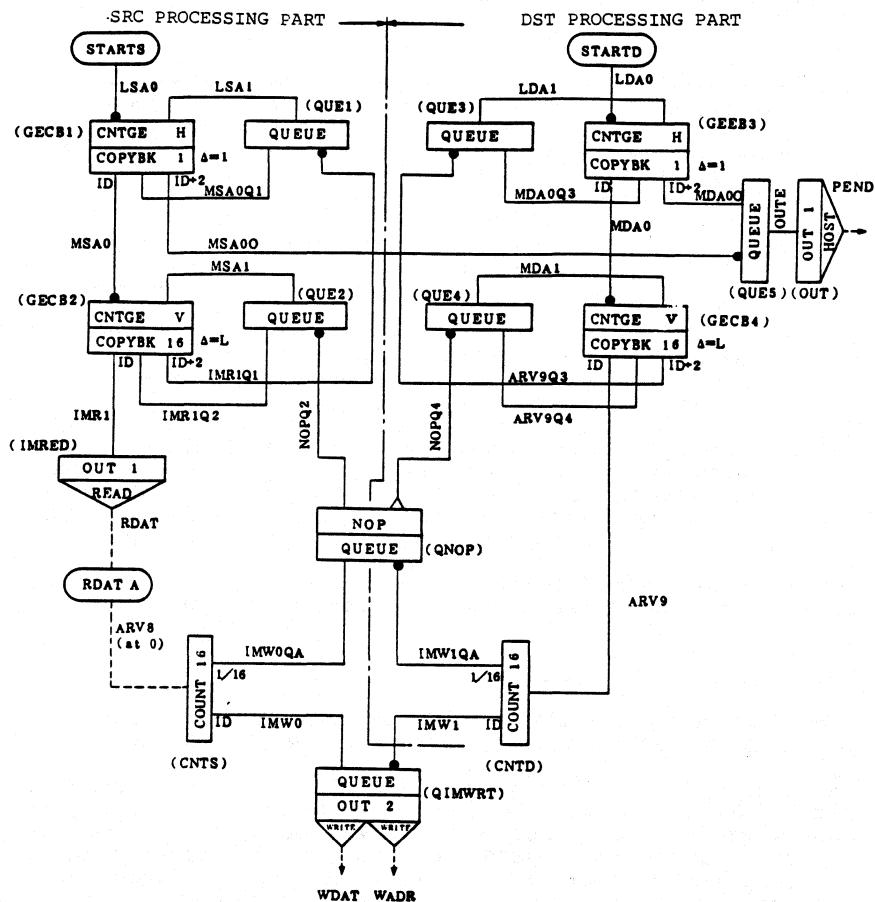

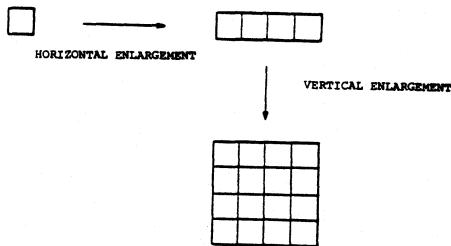

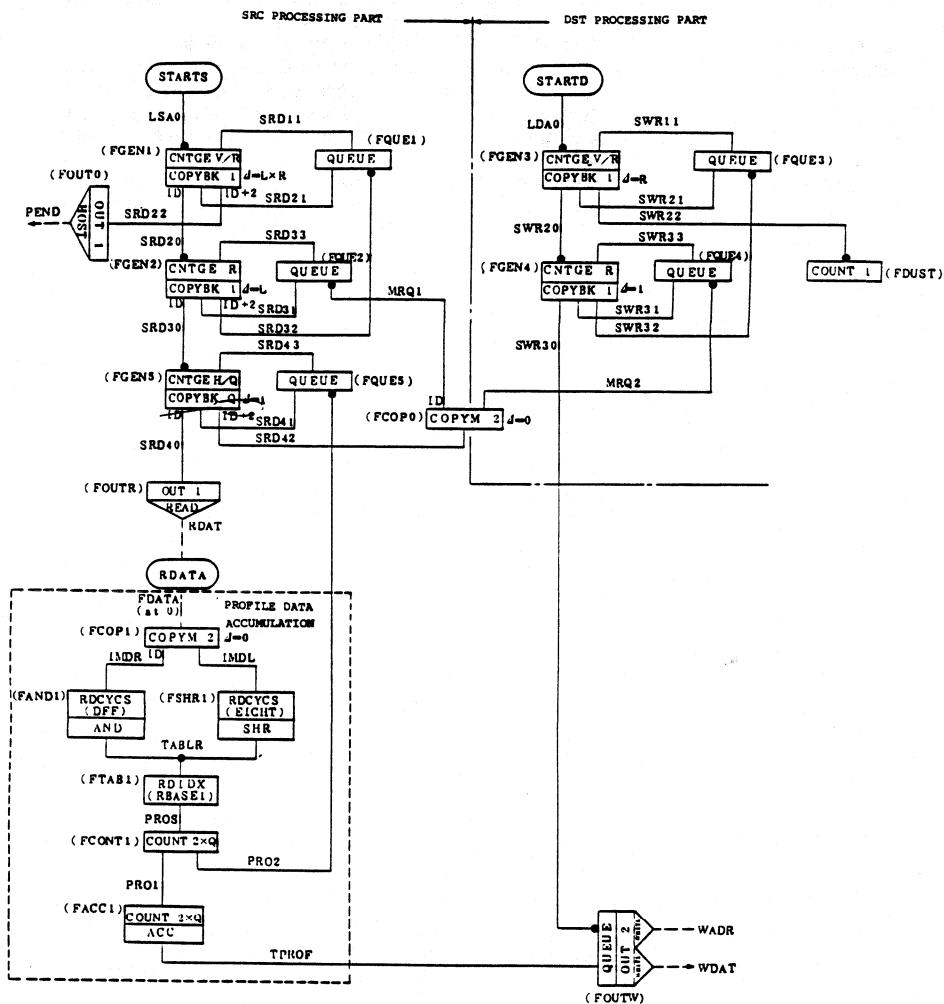

As indicated in Figure 4-6, this program consists of an SRC processing part (which reads two lines each (word unit) of SRC data and creates shrunk data) and an DST processing part (which is concerned with the generation of output addresses for the shrunk data). Each word of the shrunk data is made from four horizontally and vertically adjacent words.

The SRC processing part receives an SRC address from the host computer that serves as the starting point of the shrinking processing. Starting with that address, the SRC processing part reads two lines each of word-unit data. An OR operation is performed between the first and second lines of data that have been read, and the resulting data is alternately distributed to the high-order 8-bit and the low-order 8-bit DST data creation processing tasks.

The high-order 8-bit and the low-order 8-bit creation processing tasks look up the OR table\* on the basis of the high-order 8-bit and low-order 8-bit values received, respectively. Each then generates high-order 4-bit and low-order 4-bit data. This means 8-bit shrunk data is created by two DST words. The two 8-bit data thus generated are placed in their respective positions within the 16-bit word from which the shrunk data is generated.

The DST processing part receives a starting address from the host computer for writing the shrunk data. It generates the output addresses based on this address.

\* : This is a 4-bit data table which is made by dividing 8-bit data into 2-bit segments and by performing an OR on each of the segments.

Figure 4-6

A Four-Point OR One-Half Shrinking Flow Graph

### <Explanation of Nodes>

FNOPO : Synchronizes the actions of the start-up tokens which indicate SRC (STARTS) and DST (STARTD) addresses and sends these token to the SRC and DST processing parts.

FCOP0 : So that two lines each of SRC data can be read, generates the starting address of second line data in addition to the first line starting address (STARTS) sent by the host computer.

FGEN1/FGEN3 : Creates the starting addresses for odd/even numbered lines of SRC data on the basis of first/second line starting addresses sent from FCOP0.

FGEN2/FGEN4 : Creates addresses for SRC data lines on the basis of the addresses generated in FGEN1/FGEN3.

FOUTR0/FOUTR1 : Reads the contents of addresses generated in FGEN2/FGEN4.

FOR : Performs an OR operation between the first and second line data read in FOUTR0 and FOUTR1.

FARV1 : Distributes the OR data sent from FOR alternately between the high-order 8-bit creation and the low-order 8-bit creation processing tasks so that a horizontal OR can be performed on two 16-bit data created by performing a vertical OR (between lines), in order to generate DST data (four-point OR one-half shrunk data).

FCOP1/FCOP2 : Make two copies of the data distributed by FARV1 to provide for the fact that each of the DST high-order 8-bit and DST low-order 8-bit processing steps are comprised of high-order 4-bit and low-order 4-bit processing tasks.

FRED1, FRED3 : Performs a right 8-bit shift on OR data so that a high-order 4-bit segment can be created from the high-order 8-bit segment of 16-bit OR data by using the OR table.

FTRN1/FTRN2 : Prepares 4-bit data by looking up the OR table on the basis of the high-order/low-order 8-bit values of OR data (created by dividing eight bits into 2-bit segments and performing an OR on each of the segments).

FTRN3/FTRN4 : Prepares 4-bit data by looking up the OR table on the basis of the high-order/low-order 8-bit values of OR data (created by dividing eight bits into 2-bit segments and performing an OR on each of the segments).

FRED12/FRED08 : Prepares the high-order/low-order four bits of the high-order 8-bit DST data by performing a left 12/8 shift on the 4-bit data created in FTRN1/FTRN2.

|                          |                                                                                                                                                                               |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRED04                   | : Creates the high-order four bits of the low-order 8-bit DST data by performing a left 4-bit shift on the 4-bit data created in FTRN3.                                       |

| FADD1                    | : Creates the high-order eight bits of DST data by adding together the data generated by FRED12 and FRED08.                                                                   |

| FADD2                    | : Creates the low-order eight bits of DST data by adding together the data generated by FRED04 and FTRN4.                                                                     |

| FADD3                    | : Creates 16-bit DST data by adding together the data generated by FADD1 and FADD2.                                                                                           |

| FARV2                    | : For each 8 DST data sent from FADD3, makes two copies of the data and sends one copy to FQUEL to notify completion of the generation of the eight DST data.                 |

| FGEN5                    | : Creates M lines of addresses for H horizontal words, starting from the DST address (STARTD) sent from FNOP0.                                                                |

| FOUTW                    | : Writes the DST data generated by the SRC processing part into the DST address created in FGEN3.                                                                             |

| FADD0                    | : Modifies the address sent from FGEN5 in order to address the starting address of the next line upon completion of address generation for H horizontal words by FGEN5.       |

| FNOP1/FNOP0, FQUE0/FQUE1 | : Regulates and synchronizes the address generation by FGEN1/FGEN2, and FGEN3/FGEN4.                                                                                          |

| FWTCT                    | : Synchronizes the actions of the SRC and DST processing parts for each completion of SRC and DST addresses (i.e., first and second line addresses) for one line of DST data. |

| FCOP3                    | : Notifies the SRC and DST processing parts of the completion of addresses for one line of DST data by the SRC and DST processing parts.                                      |

| FWTVN                    | : Synchronizes completion of all addresses by the SRC and DST processing parts.                                                                                               |

| PEND                     | : Notifies the host computer of completion of generation for all addresses for a reduction processing task.                                                                   |

| SRC Data             | Simple One-Half Shrinking Table<br>(Note 1) | Four-Point OR One-Half Shrinking Table<br>(Note 2) |

|----------------------|---------------------------------------------|----------------------------------------------------|

| Bits 7 6 5 4 3 2 1 0 | Table Data                                  | Table Data                                         |

| 0 0 0 0 0 0 0 0      | 0 0 0 0                                     | 0 0 0 0                                            |

| 0 0 0 0 0 0 0 1      | 0 0 0 1                                     | 0 0 0 1                                            |

| 0 0 0 0 0 0 1 0      | 0 0 0 0                                     | 0 0 0 1                                            |

| 0 0 0 0 0 0 1 1      | 0 0 0 1                                     | 0 0 0 1                                            |

| 0 0 0 0 0 1 0 0      | 0 0 1 0                                     | 0 0 1 0                                            |

| :                    | :                                           | :                                                  |

| :                    | :                                           | :                                                  |

| 1 0 1 1 1 0 0 1      | 0 1 0 1                                     | 1 1 1 1                                            |

| 1 0 1 1 1 0 1 0      | 0 1 0 0                                     | 1 1 1 1                                            |

| 1 0 1 1 1 0 1 1      | 0 1 0 1                                     | 1 1 1 1                                            |

| :                    | :                                           | :                                                  |

| 1 1 1 1 1 1 1 1      | 1 1 1 1                                     | 1 1 1 1                                            |

Note 1: The odd-numbered bits are ignored.

7 6 5 4 3 2 1 0

+-----+-----+-----+-----+

| # # | # # | # # | # # |

+-----+-----+-----+-----+

Only these bits are eliminated.

Note 2: An OR is performed between the odd-numbered and even-numbered bits.

7 6 5 4 3 2 1 0

+-----+-----+-----+-----+

| + + + + + + + + |

+-----+-----+-----+-----+

\ \ \ \ \ \ \ \ \ / / / /

OR OR OR OR OR

Each of these groups is ORed.

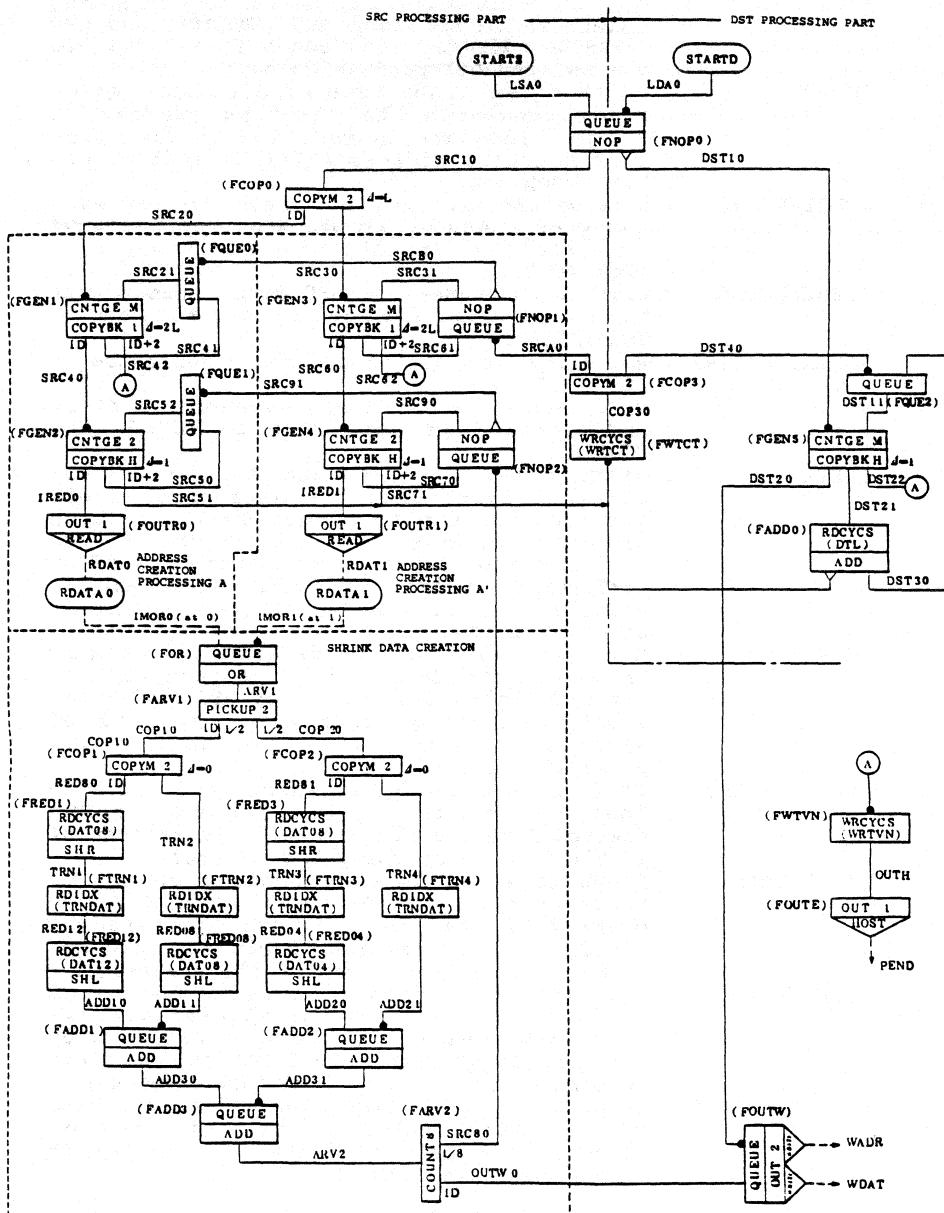

#### 4.2.5 Tips on Writing Flow Graphs

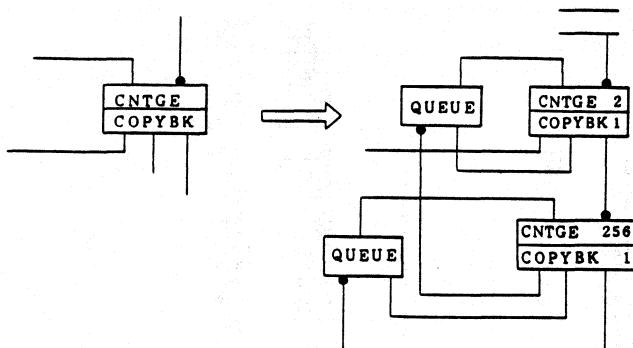

Although the QUEUE instruction is normally employed in synchronizing various activities, in some cases the WRCYCS and WRCYCL instructions are used (as in the case of the FWTCT and FWTVN nodes in this program).

When BS (buffer size) = WC (write counter), the FTRC = 1 token does not vanish in either the WRCYCS or WRCYCL instruction. When there are many data senders and you wish to synchronize various actions including those of the senders, the flow graph should be constructed in the manner indicated in the figure below.

**Notice that in this case  $n$  words in the DM (Data Memory) must be assigned as dummy data.**

#### 4.2.6 Assembler Source Listing

```

1: ****

2: :

3: :      SHRINK 1/2 (4 POINT OR )

4: :

5: -----

6: :

7: MODULE IPP      =      8      :

8: :

9: EQUATE L      =      64      :

10: EQUATE M      =      256      :

11: EQUATE H      =      16      :

12: :

13: EQUATE HOST    =      8      :

14: EQUATE READ     =      4      :

15: EQUATE WRITE    =      5      :

16: :

17: EQUATE STARTS   =      8      :

18: EQUATE STARTD   =      32      :

19: :

20: ****

21: :

22: :      INPUT-OUTPUT

23: :

24: -----

25: :

26: INPUT  LSA0,  LDA0,  IMOR0 AT 0,  IMOR1 AT 1      :

27: :

28: OUTPUT RDAT0,  RDAT1,  WDAT,  WADR,  PEND      :

29: :

30: ****

31: :

32: :      LINK TABLE

33: :

34: -----

35: :

36: LINK  SRC10,  DST10      =      FNOP0  (LSA0,  LDA0      )

37: LINK  SRC20,  SRC30      =      FCOP0  (SRC10      )

38: LINK  DST20,  DST21,  DST22      =      FGEN5  (DST11,  DST10      )

39: LINK  SRC40,  SRC41,  SRC42      =      FGEN1  (SRC21,  SRC20      )

40: LINK  SRC60,  SRC61,  SRC62      =      FGEN3  (SRC31,  SRC30      )

41: LINK  IRED0,  SRC50,  SRC51      =      FGEN2  (SRC52,  SRC40      )

42: LINK  SRC21      =      FQUE0  (SRC41,  SRC80      )

43: LINK  OUTH      =      FWTVN  (      .SRC42      )

44: LINK  RDAT0      =      FOUTR0  (IRED0      )

45: LINK  SRC52      =      FQUE1  (SRC50,  SRC91      )

46: LINK  COP30      =      FUTCT  (      .SRC51      )

47: LINK  IRED1,  SRC70,  SRC71      =      FGEN4  (SRC90,  SRC60      )

48: LINK  SRC31,  SRC80      =      FNOP1  (SRC61,  SRC40      )

49: LINK  OUTH      =      FWTVN  (      .SRC62      )

50: LINK  RDAT1      =      FOUTR1  (IRED1      )

51: LINK  SRC90,  SRC91      =      FNOP2  (SRC70,  SRC80      )

52: LINK  COP30      =      FUTCT  (      .SRC71      )

53: LINK  ARV1      =      FOR   (IMOR0,  IMOR1      )

54: LINK  COP10,  COP20      =      FARV1  (ARV1      )

55: LINK  RED00,  TRN2      =      FCOP1  (COP10      )

56: LINK  TRN1      =      FRED1  (RED00      )

57: LINK  RED12      =      FTRN1  (TRN1      )

58: LINK  ADD10      =      FRED12  (RED12      )

59: LINK  RED00      =      FTRN2  (TRN2      )

60: LINK  ADD11      =      FRED08  (RED00      )

```

```

61: LINK ADD30      == FADD1  (ADD10, ADD11  )

62: LINK RED81, TRN4 == FCOP2  (COP20

63: LINK TRN3      == FRED3  (RED81

64: LINK RED84      == FTRN3  (TRN3

65: LINK ADD20      == FRED84 (RED84

66: LINK ADD21      == FTRN4  (TRN4

67: LINK ADD31      == FADD2  (ADD20, ADD21  )

68: LINK ARV2      == FADD3  (ADD30, ADD31  )

69: LINK OUTW, SRC80 == FARV2  (ARV2

70: LINK WDAT, WADR == FOUTW  (OUTW, DST20  )

71: LINK DST30, DST31 == FADD8  (DST21

72: LINK OUTH      == FUTVN  (DST22

73: LINK DST11      == FQUE2  (DST30, DST40  )

74: LINK COP30      == FWCTC  (DST40, DST31  )

75: LINK SRC80, DST40 == FCOP3  (COP30

76: LINK PEND      == FOUTE  (OUTH

77:

78: ****

79:

80: : FUNCTION TABLE

81:

82: -----

83:

84: FUNCTION FOUTR0 == OUT1   (READ, 0)

85: FUNCTION FOUTR1 == OUT1   (READ, 1)

86: FUNCTION FOUTW  == OUT2   (WRTIE, 20H, 0).QUEUE (QUEW, 16)

87: FUNCTION FOUTE  == OUT1   (HOST, 0)

88: FUNCTION FGEN1  == COPYBK (1, 2*L), CNTGE (M)

89: FUNCTION FGEN2  == COPYBK (1, 1), CNTGE (2)

90: FUNCTION FGEN3  == COPYBK (1, 2*L), CNTGE (M)

91: FUNCTION FGEN4  == COPYBK (1, 1), CNTGE (2)

92: FUNCTION FGEN5  == COPYBK (1, 1), CNTGE (M)

93: FUNCTION FCOP0  == COPYM (2, L)

94: FUNCTION FCOP1  == COPYM (2, 0)

95: FUNCTION FCOP2  == COPYM (2, 0)

96: FUNCTION FCOP3  == COPYM (2, 0)

97: FUNCTION FARV1  == PICKUP (2)

98: FUNCTION FARV2  == COUNT (8)

99: FUNCTION FRED1  == SHR   (X, ), RDCYCS (DAT88, 1)

100: FUNCTION FRED3  == SHR   (X, ), RDCYCS (DAT88, 1)

101: FUNCTION FRED12 == SHL   (X, ), RDCYCS (DAT12, 1)

102: FUNCTION FRED88 == SHL   (X, ), RDCYCS (DAT88, 1)

103: FUNCTION FRED84 == SHL   (X, ), RDCYCS (DAT84, 1)

104: FUNCTION FTRN1  == RDIDX (TRNDAT)

105: FUNCTION FTRN2  == RDIDX (TRNDAT)

106: FUNCTION FTRN3  == RDIDX (TRNDAT)

107: FUNCTION FTRN4  == RDIDX (TRNDAT)

108: FUNCTION FADD0  == ADD   (XY, ), RDCYCS (DTL, 1)

109: FUNCTION FADD1  == ADD   (X, ), QUEUE (QUE6, 8)

110: FUNCTION FADD2  == ADD   (X, ), QUEUE (QUE7, 8)

111: FUNCTION FADD3  == ADD   (X, ), QUEUE (QUE8, 8)

112: FUNCTION FNOP0  == NOP   (XY, ), QUEUE (QUE3, 1)

113: FUNCTION FNOP1  == NOP   (XY, ), QUEUE (QUE4, 1)

114: FUNCTION FNOP2  == NOP   (XY, ), QUEUE (QUE5, 1)

115: FUNCTION FQUE0  == QUEUE (QUE0, 1)

116: FUNCTION FQUE1  == QUEUE (QUE1, 1)

117: FUNCTION FQUE2  == QUEUE (QUE2, 1)

118: FUNCTION FWCTC  == WRCYCS (WRTCT, 3)

119: FUNCTION FUTVN  == WRCYCS (WRTVN, 3)

120: FUNCTION FOR   == OR    (X, ), QUEUE (QUE9, 16)

```

## 4.3 Neighboring 16-Point Addition One-Quarter Shrinking

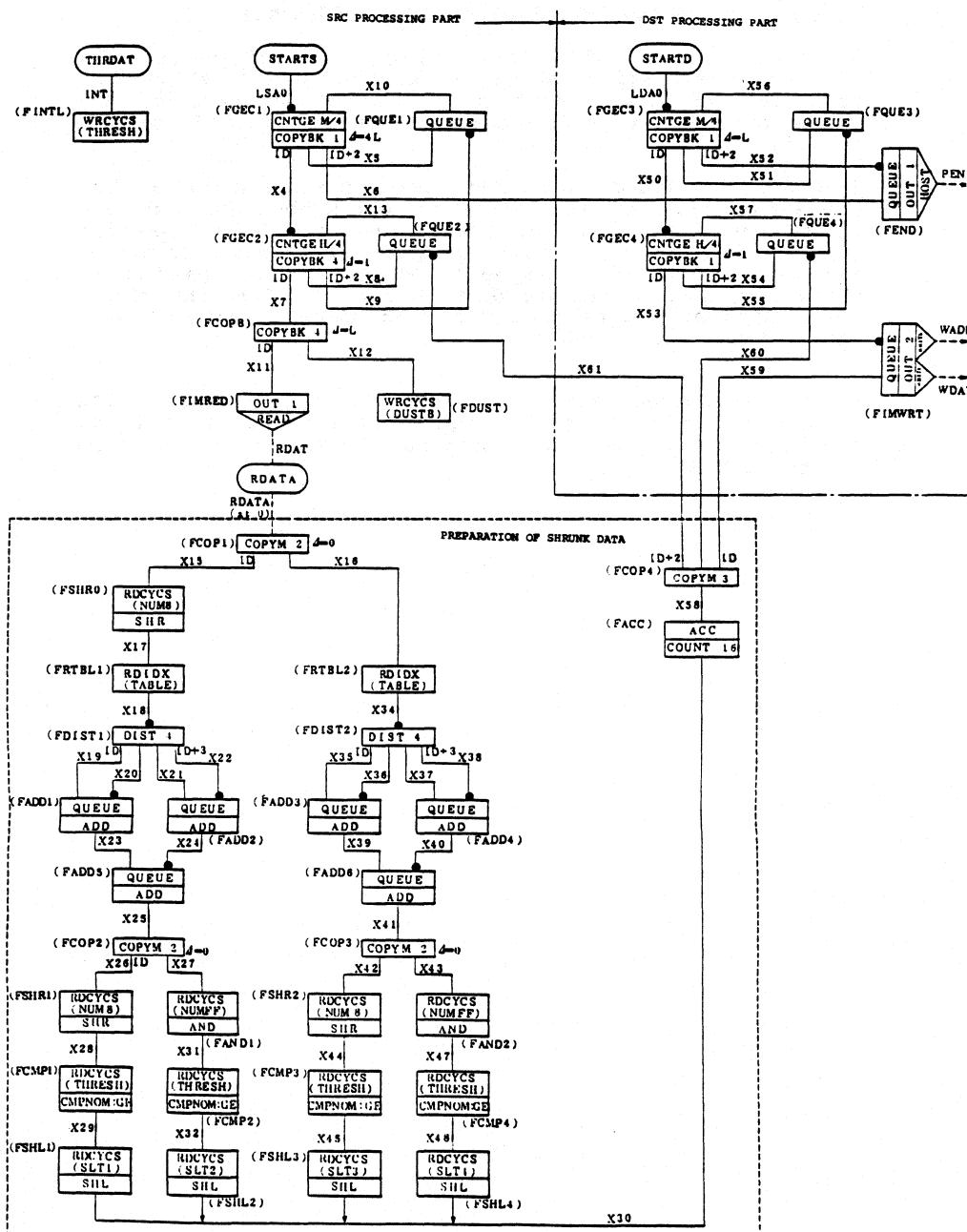

### 4.3.1 Processing Explained

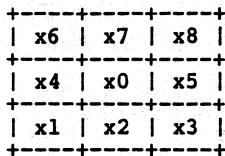

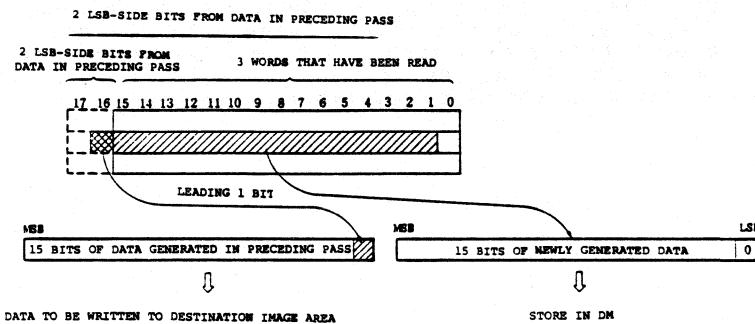

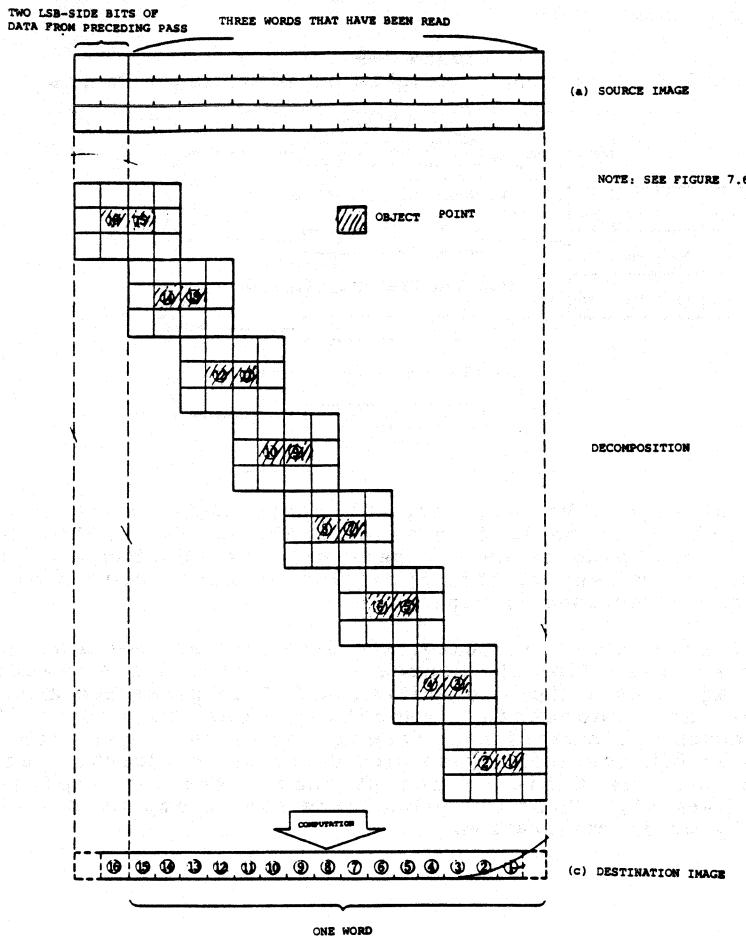

A one-quarter shrinking involves shrinking 4 horizontal and 4 vertical bits, for a total of 15 bits, into one bit. In this neighboring 16-point addition reduction, the number of "1"s in the 16-bit data are counted and shrunk data is set to "1" if the sum is greater than a given value and "0" otherwise.

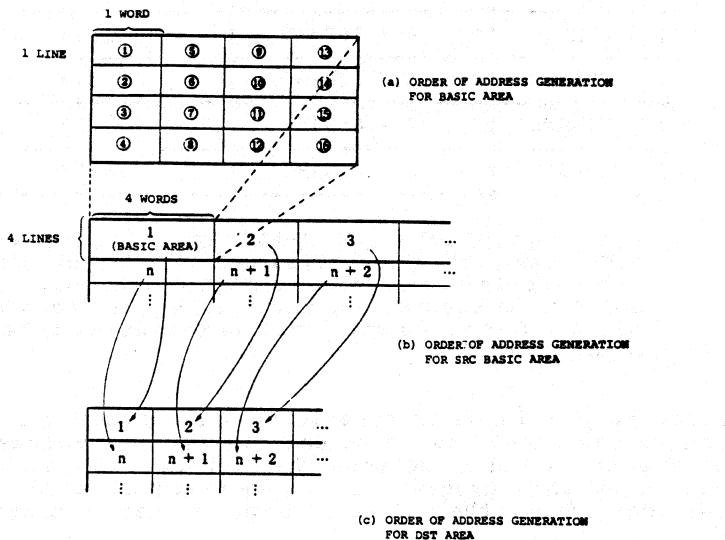

The basic size of source image area (SRC) that can be shrunk by this program is four horizontal words by four vertical words, as shown in Figure 4-7. This is because the destination image area (DST) is addressed in word units.

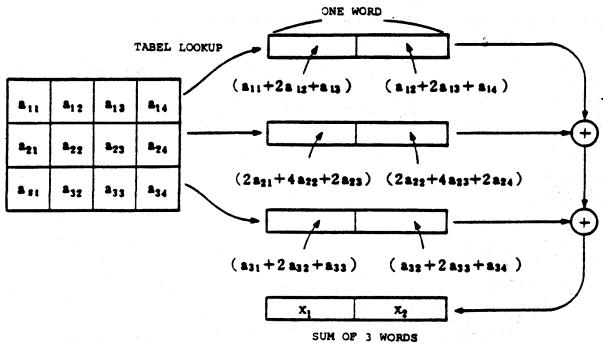

### 4.3.2 Algorithm

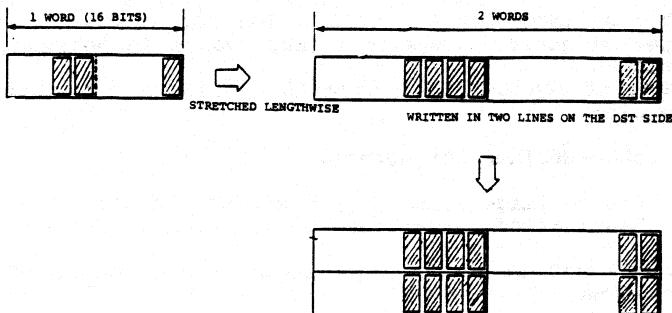

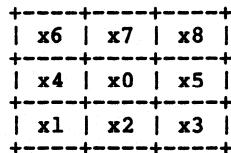

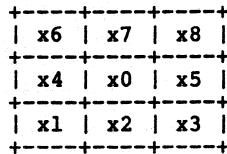

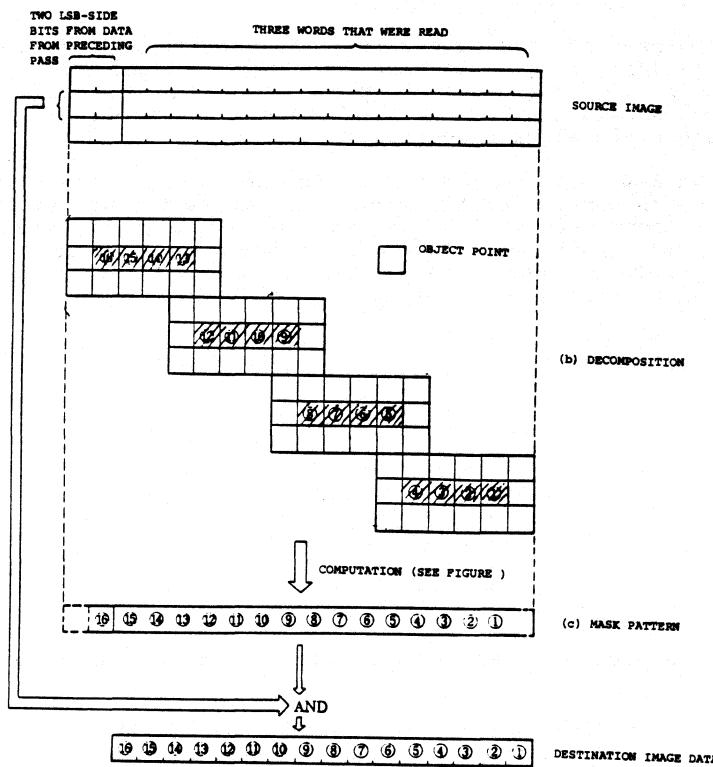

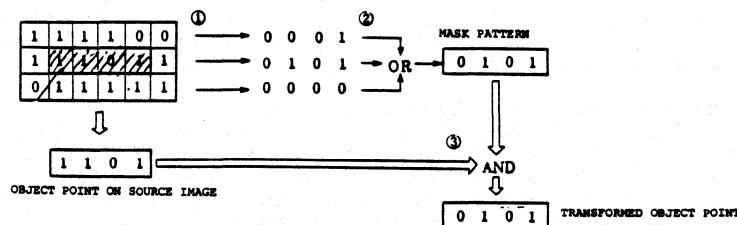

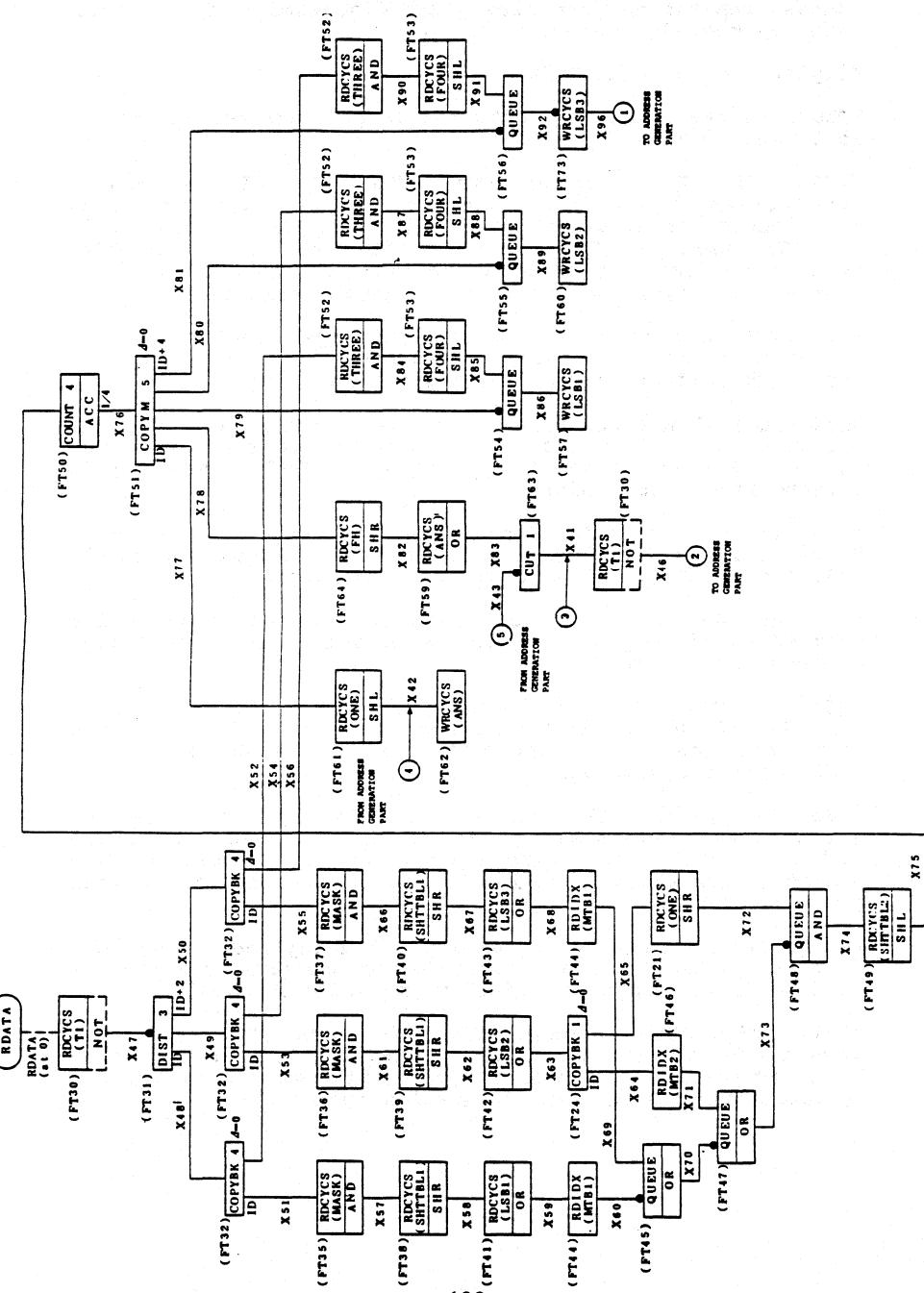

The number of "1"s contained in a given 16-bit data, four bits by four lines, is counted. If the number is number is greater than or equal to a threshold value, the shrunk data bit is set to "1"; otherwise, it is set to "0". The counting is done by a table lookup.